AMD Am29000 - AMD Am29000

O AMD Am29000 , comumente abreviado para 29k , é uma família de microprocessadores e microcontroladores RISC de 32 bits desenvolvidos e fabricados pela Advanced Micro Devices (AMD). Com base no seminal RISC de Berkeley , o 29k adicionou uma série de melhorias significativas. Eles foram, por um tempo, os chips RISC mais populares do mercado, amplamente utilizados em impressoras a laser de diversos fabricantes.

Várias versões foram introduzidas durante o período de 1988 a 1995, começando com o 29000. O modelo final, o 29050 , foi a primeira versão superescalar , desativando até quatro instruções por ciclo e também incluindo uma unidade de ponto flutuante (FPU) bastante aprimorada .

No final de 1995, a AMD abandonou o desenvolvimento do 29k porque a equipe de design foi transferida para oferecer suporte ao lado do PC dos negócios. O que restou dos negócios integrados da AMD foi realinhado para a família 186 de derivados 80186 integrados . A maioria dos recursos da AMD foi então concentrada em seus clones de desktop x86 de alto desempenho, usando muitas das idéias e partes individuais dos 29k mais recentes para produzir o AMD K5 .

Projeto

O 29000 evoluiu do mesmo design Berkeley RISC que também levou ao Sun SPARC , Intel i960 , ARM e RISC-V .

Um elemento de design usado em alguns dos designs derivados de Berkeley RISC é o conceito de janelas de registro , uma técnica usada para acelerar significativamente as chamadas de procedimento . A ideia é usar um grande conjunto de registradores como pilha, carregando dados locais em um conjunto de registradores durante uma chamada e marcando-os como "mortos" quando o procedimento retornar. Os valores retornados das rotinas seriam colocados na "página global", os oito primeiros registros do SPARC (por exemplo). O projeto RISC concorrente da Universidade de Stanford , o Stanford MIPS , também analisou esse conceito, mas decidiu que compiladores aprimorados poderiam fazer um uso mais eficiente de registradores de propósito geral do que uma janela com fio.

No design original de Berkeley, SPARC e i960, o tamanho das janelas era fixo. Uma rotina usando apenas uma variável local ainda usaria até oito registradores no SPARC, desperdiçando esse recurso caro. Foi aqui que o 29000 diferiu desses designs anteriores, usando um tamanho de janela variável. Neste exemplo, apenas dois registradores seriam usados, um para a variável local e outro para o endereço de retorno . Ele também adicionou mais registros, incluindo os mesmos 128 registros para a pilha de procedimentos, mas adicionando outros 64 para acesso global. Em comparação, o SPARC tinha 128 registros no total, e o conjunto global era uma janela padrão de oito. Essa mudança resultou em um uso de registro muito melhor no 29000 sob uma ampla variedade de cargas de trabalho.

O 29000 também estendeu a pilha da janela de registro com uma pilha na memória (e, em teoria, no cache). Quando a janela fosse preenchida, as chamadas seriam empurradas do final da pilha de registros para a memória, restauradas conforme necessário quando a rotina retornasse. Geralmente, o uso do registro do 29000 era consideravelmente mais avançado do que os designs concorrentes baseados nos conceitos de Berkeley.

Outra diferença com o design de Berkeley é que o 29000 não incluiu nenhum registro de código de condição para fins especiais. Qualquer registro pode ser usado para este propósito, permitindo que as condições sejam facilmente salvas à custa de complicar algum código. Um buffer de pré-busca de instrução ("Branch Target Cache") foi usado para armazenar até 4 instruções e foi usado para melhorar o desempenho durante os branches - o 29000 não incluía nenhum sistema de previsão de branch, então havia um atraso se um branch fosse tomado (nem foi era originalmente superescalar , portanto não podia "fazer os dois lados", como é comum em alguns projetos). O buffer atenuou isso armazenando quatro instruções do outro lado da ramificação, que podiam ser executadas instantaneamente enquanto o buffer era recarregado com novas instruções da memória.

Versões

O primeiro 29000 foi lançado em 1988, incluindo um MMU embutido, mas o suporte de ponto flutuante foi transferido para o 29027 FPU . As unidades com MMU ou cache de destino de filial com falha foram vendidas como 29005 .

A linha foi atualizada com o 29030 e o 29035 , que incluíam 8 KB ou 4 KB de cache de instruções, respectivamente. Outra atualização integrou a FPU na matriz e adicionou um cache de dados de 4 KB para produzir o 29040 .

A última versão de uso geral foi o 29050 . Esta foi uma atualização significativa do projeto original, a primeira versão superescalar que podia executar instruções fora de ordem e especulativamente . Até seis instruções poderiam ser trabalhadas ao mesmo tempo em vários estágios do pipeline, e quatro poderiam ser retiradas em qualquer ciclo. O 29050 também incluiu uma FPU significativamente melhorada. O 29050 estava inicialmente disponível com taxas de clock de 25, 50 e 75 MHz . Uma versão de 100 MHz foi introduzida posteriormente.

Várias partes do design do 29050 foram usadas como base para a série K5 de processadores compatíveis com x86 . O somador e multiplicador FPU foram transportados com algumas alterações de layout, um mecanismo de nanocódigo foi adicionado ao FPU para acomodar as instruções complexas encontradas em x86, mas não no 29050, enquanto o resto do design do núcleo foi usado junto com microcódigo complexo para traduzir x86 instruções para 29k-like 'µops' em tempo real.

A Honeywell 29KII é uma CPU baseada no AMD 29050 e foi amplamente usada em aviônicos em tempo real.

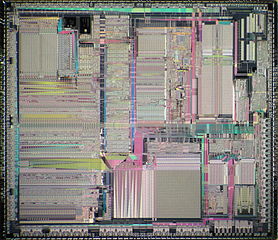

- Morrer fotos

Veja também

Referências

links externos

- Guia de ID AMD 29k (Processador de Instrução Simplificado)

- Mann, Daniel (1995), Evaluating and Programming the 29K RISC Family (PDF) , Advanced Micro Devices, arquivado do original (PDF) em 27 de setembro de 2007 livro pdf sobre família 29k

- chipdb.org Imagens de diferentes processadores Am29000