Tecnologia MOS 6502 - MOS Technology 6502

Um processador MOS Technology 6502 em um pacote de plástico DIP-40 . O código de data de quatro dígitos indica que foi feito na 45ª semana (novembro) de 1985.

| |

| Informação geral | |

|---|---|

| Lançado | 1975 |

| Fabricante (s) comum (is) | |

| atuação | |

| Máx. Taxa de clock da CPU | 1 MHz a 3 MHz |

| Largura de dados | 8 |

| Largura do endereço | 16 |

| Arquitetura e classificação | |

| Conjunto de instruções | MOS 6502 |

| Instruções | 56 |

| Especificações físicas | |

| Transistores | |

| Pacote (s) | |

| História | |

| Antecessor | |

| Sucessor | |

O MOS Technology 6502 (normalmente pronunciado "sessenta-cinco-zero-dois" ou "seis-cinco-zero-dois") é um microprocessador de 8 bits que foi projetado por uma pequena equipe liderada por Chuck Peddle para a MOS Technology . A equipe de design já havia trabalhado na Motorola no projeto do Motorola 6800 ; o 6502 é essencialmente uma versão simplificada, mais barata e mais rápida desse design.

Quando foi lançado em 1975, o 6502 era o microprocessador mais barato do mercado por uma margem considerável. Inicialmente, ele foi vendido por menos de um sexto do custo de designs concorrentes de empresas maiores, como o 6800 ou o Intel 8080 . Sua introdução causou quedas rápidas nos preços em todo o mercado de processadores. Junto com o Zilog Z80 , ele deu início a uma série de projetos que resultaram na revolução do computador doméstico no início dos anos 1980.

Os consoles de videogame e computadores populares, como o Atari 2600 , família Atari de 8 bits , Apple II , Nintendo Entertainment System , Commodore 64 , Atari Lynx , BBC Micro e outros, usam o 6502 ou variações do design básico. Logo após o lançamento do 6502, a MOS Technology foi comprada pela Commodore International , que continuou a vender o microprocessador e as licenças a outros fabricantes. Nos primeiros dias do 6502, foi terceirizado pela Rockwell e Synertek , e posteriormente licenciado para outras empresas.

Em sua forma CMOS (o 65C02 , que foi desenvolvido pelo Western Design Center ), a família 6502 continua a ser amplamente utilizada em sistemas embarcados , com volumes de produção estimados em centenas de milhões.

História e uso

Origins na Motorola

O 6502 foi projetado por muitos dos mesmos engenheiros que projetaram a família de microprocessadores Motorola 6800 . A Motorola iniciou o projeto do microprocessador 6800 em 1971 com Tom Bennett como o arquiteto principal. O layout do chip começou no final de 1972, os primeiros 6800 chips foram fabricados em fevereiro de 1974 e toda a família foi oficialmente lançada em novembro de 1974. John Buchanan foi o projetista do chip 6800 e Rod Orgill, que mais tarde fez o 6501, ajudou Buchanan com análises de circuito e layout de chip. Bill Mensch ingressou na Motorola em junho de 1971, após se formar na Universidade do Arizona (aos 26 anos). Sua primeira tarefa foi ajudar a definir os ICs periféricos para a família 6800 e, mais tarde, ele foi o principal projetista do 6820 Peripheral Interface Adapter (PIA). Os engenheiros da Motorola podiam executar simulações analógicas e digitais em um computador mainframe IBM 370-165 . Bennett contratou Chuck Peddle em 1973 para fazer o trabalho de suporte arquitetônico nos produtos da família 6800 já em andamento. Ele contribuiu em muitas áreas, incluindo o design do 6850 ACIA (interface serial).

Os clientes-alvo da Motorola eram empresas eletrônicas estabelecidas, como Hewlett-Packard , Tektronix , TRW e Chrysler . Em maio de 1972, os engenheiros da Motorola começaram a visitar clientes selecionados e compartilhar os detalhes de seu sistema de microprocessador de 8 bits proposto com ROM, RAM, interfaces paralelas e seriais. No início de 1974, eles forneceram amostras de engenharia dos chips para que os clientes pudessem fazer o protótipo de seus projetos. A estratégia de "família total de produtos" da Motorola não se concentrava no preço do microprocessador, mas na redução do custo total de design do cliente. Eles ofereceram software de desenvolvimento em um computador timeshare, o sistema de depuração "EXORciser", treinamento no local e suporte de engenheiro de aplicação de campo. Tanto a Intel quanto a Motorola haviam anunciado inicialmente um preço de US $ 360 por um único microprocessador. O preço real das quantidades de produção era muito menor. A Motorola ofereceu um kit de design contendo o 6800 com seis chips de suporte por US $ 300.

Peddle, que acompanhava os vendedores nas visitas aos clientes, descobriu que os clientes ficavam desanimados com o alto custo dos chips do microprocessador. Ao mesmo tempo, essas visitas invariavelmente resultavam nos engenheiros que ele apresentava para produzir listas de instruções necessárias que eram muito menores do que "todas essas instruções sofisticadas" que haviam sido incluídas no 6800. Peddle e outros membros da equipe começaram a delinear o projeto de um recurso aprimorado, microprocessador de tamanho reduzido. Naquela época, a nova instalação de fabricação de semicondutores da Motorola em Austin, Texas, estava tendo dificuldade para produzir chips MOS, e meados de 1974 foi o início de uma recessão de um ano na indústria de semicondutores. Além disso, muitos funcionários de Mesa, Arizona, ficaram descontentes com a mudança para Austin, Texas .

A gerência da Divisão de Produtos de Semicondutores da Motorola estava sobrecarregada de problemas e não demonstrou interesse na proposta de microprocessador de baixo custo de Peddle. Por fim, Peddle recebeu uma carta oficial dizendo-lhe para parar de trabalhar no sistema. Peddle respondeu ao pedido informando à Motorola que a carta representava uma declaração oficial de "abandono do projeto" e, como tal, a propriedade intelectual que ele havia desenvolvido até então era sua. Em uma entrevista em novembro de 1975, o presidente da Motorola, Robert Galvin, finalmente concordou que o conceito de Peddle era bom e que a divisão perdeu uma oportunidade: "Não escolhemos os líderes certos na divisão de produtos de semicondutores." A divisão foi reorganizada e a gestão substituída. O novo vice-presidente do grupo, John Welty, disse: "A organização de vendas de semicondutores perdeu sua sensibilidade às necessidades do cliente e não pôde tomar decisões rápidas."

Mudança para a tecnologia MOS

Peddle começou a procurar fora da Motorola uma fonte de financiamento para este novo projeto. Ele inicialmente abordou o CEO da Mostek , LJ Sevin , mas ele recusou. Sevin admitiu mais tarde que isso era porque ele temia que a Motorola os processasse.

Enquanto Peddle estava visitando a Ford Motor Company em uma de suas viagens de vendas, Bob Johnson, mais tarde chefe da divisão de automação de motores da Ford, mencionou que seu ex-colega John Paivinen havia se mudado para a General Instrument e aprendeu sozinho design de semicondutores. Desde então, ele mudou-se e estava fazendo um trabalho muito interessante com chipsets de calculadora em uma nova empresa que formou em Valley Forge, Pensilvânia .

Paivinen formou a MOS Technology em 1969 com dois outros executivos da General Instrument, Mort Jaffe e Don McLaughlin. A Allen-Bradley , fornecedora de componentes eletrônicos e controles industriais, adquiriu participação majoritária em 1970. A empresa projetou e fabricou CIs personalizados para clientes e desenvolveu uma linha de chips calculadores.

Depois que os esforços de Mostek fracassaram, Peddle abordou Paivinen, que "entendeu imediatamente". Em 19 de agosto de 1974, Chuck Peddle, Bill Mensch, Rod Orgill, Harry Bawcom, Ray Hirt, Terry Holdt e Wil Mathys deixaram a Motorola para ingressar na MOS. Mike Janes juntou-se mais tarde. Dos dezessete designers de chips e pessoas de layout da equipe 6800, oito saíram. O objetivo da equipe era projetar e produzir um microprocessador de baixo custo para aplicativos incorporados e atingir a maior base de clientes possível. Isso só seria possível se o microprocessador fosse de baixo custo e a equipe definisse a meta de preço em US $ 5 em volume. Mensch afirmou mais tarde que o objetivo não era o preço do processador em si, mas criar um conjunto de chips que pudesse ser vendido a US $ 20 para competir com o recém-lançado Intel 4040, vendido por US $ 29 em um chipset completo semelhante.

Os chips são produzidos imprimindo várias cópias do design do chip na superfície de um "wafer" , um disco fino de silício altamente puro. Chips menores podem ser impressos em números maiores no mesmo wafer, diminuindo seu preço relativo. Além disso, os wafers sempre incluem alguns pequenos defeitos físicos que estão espalhados pela superfície. Qualquer chip impresso nesse local irá falhar e deve ser descartado. Chips menores significam que qualquer cópia tem menos probabilidade de ser impressa em um defeito. Por ambas as razões, o custo do produto final depende fortemente do tamanho do design do chip.

Os 6800 chips originais deveriam ter 180 × 180 mils (4,6 × 4,6 mm) , mas o layout foi concluído em 212 × 212 mils (5,4 × 5,4 mm) , ou uma área de 29,0 mm 2 . Para o novo design, a meta de custo exigia uma meta de tamanho de 153 × 168 mils (3,9 × 4,3 mm) , ou uma área de 16,6 mm 2 . Várias novas técnicas seriam necessárias para atingir esse objetivo.

Mudança para NMOS

Dois avanços significativos chegaram ao mercado no momento em que o 6502 estava sendo projetado, o que proporcionou reduções de custo significativas. O primeiro foi a mudança para NMOS de carga de depleção . O 6800 usava um processo NMOS anterior que exigia três tensões de alimentação, mas um dos recursos do chip era um dobrador de tensão integrado que permitia que uma única fonte de + 5V fosse usada para +5, -5 e +12 internamente, ao contrário de outros chips de a era como o Intel 8080, que exigia três pinos de alimentação separados. Embora esse recurso reduzisse a complexidade da fonte de alimentação e do layout dos pinos, ainda exigia trilhos de alimentação separados para as várias portas do chip, aumentando a complexidade e o tamanho. Ao mudar para o novo design de carga de depleção, um único suprimento +5 era tudo o que era necessário, eliminando toda essa complexidade.

Uma outra vantagem prática era que o sinal do clock para CPUs anteriores tinha que ser forte o suficiente para sobreviver a toda a dissipação enquanto viajava pelos circuitos, o que quase sempre exigia um chip externo separado que pudesse fornecer um sinal forte o suficiente. Com os requisitos de energia reduzidos do NMOS, o relógio pode ser movido para o chip, simplificando o design geral do computador. Essas mudanças reduziram muito a complexidade e o custo de implementação de um sistema completo.

Outra mudança que estava ocorrendo era a introdução do mascaramento de projeção. Anteriormente, os chips eram padronizados na superfície do wafer colocando uma máscara na superfície do wafer e, em seguida, direcionando uma luz brilhante sobre ela. As máscaras geralmente pegam pequenos pedaços de sujeira ou fotorresiste à medida que são retiradas do chip, causando falhas nesses locais em qualquer máscara subsequente. Com projetos complexos como CPUs, 5 ou 6 dessas etapas de mascaramento seriam usadas, e a chance de que pelo menos uma dessas etapas introduzisse uma falha era muito alta. Na maioria dos casos, 90% desses projetos apresentavam falhas, resultando em um rendimento de 10%. O preço das amostras de trabalho tinha que cobrir o custo de produção dos 90% que eram jogados fora.

Em 1973, Perkin-Elmer introduziu o sistema Micralign , que projetava uma imagem da máscara no wafer em vez de requerer contato direto. As máscaras não pegavam mais sujeira dos wafers e duravam na ordem de 100.000 usos em vez de 10. Isso eliminou as falhas graduais e as altas taxas de falhas vistas anteriormente em projetos complexos. Os rendimentos em CPUs saltaram imediatamente de 10% para 60 ou 70%. Isso significa que o preço da CPU caiu aproximadamente na mesma quantidade e o microprocessador de repente se tornou um dispositivo comum.

As linhas de fabricação existentes da MOS Technology eram baseadas na tecnologia PMOS mais antiga, eles ainda não tinham começado a trabalhar com NMOS quando a equipe chegou. Paivinen prometeu ter uma linha NMOS instalada e funcionando a tempo de iniciar a produção da nova CPU. Ele cumpriu a promessa, a nova linha estava pronta em junho de 1975.

Notas de design

Chuck Peddle, Rod Orgill e Wil Mathys projetaram a arquitetura inicial dos novos processadores. Um artigo de setembro de 1975 na revista EDN fornece este resumo do design:

A família MOS Technology 650X representa uma tentativa consciente de oito ex-funcionários da Motorola que trabalharam no desenvolvimento do sistema 6800 para lançar uma peça que substituiria e superaria o 6800, mas com vendas inferiores. Com o benefício da retrospectiva obtida no projeto 6800, a equipe de Tecnologia MOS liderada por Chuck Peddle, fez as seguintes alterações arquitetônicas na CPU da Motorola…

A principal mudança em termos de tamanho do chip foi a eliminação dos drivers tri-state das saídas do barramento de endereço. Isso foi incluído no 6800 para permitir que funcione com outros chips em funções de acesso direto à memória (DMA) e coprocessamento, ao custo de um espaço significativo do molde. Na prática, o uso de tal sistema exigia que os outros dispositivos fossem igualmente complexos e, em vez disso, os projetistas tendiam a usar sistemas fora do chip para coordenar esse acesso. O 6502 simplesmente removeu esse recurso, mantendo seu design como um controlador barato sendo usado para tarefas específicas e se comunicando com dispositivos simples. Peddle sugeriu que qualquer pessoa que realmente precisasse desse estilo de acesso poderia implementá-lo com um único 74158 .

A próxima grande diferença foi simplificar os registros. Para começar, um dos dois acumuladores foi removido. Registradores de uso geral, como acumuladores, precisam ser acessados por muitas partes do decodificador de instruções e, portanto, requerem uma quantidade significativa de fiação para mover os dados de e para seu armazenamento. Dois acumuladores tornam muitas tarefas de codificação mais fáceis, mas custam ao próprio design do chip uma complexidade significativa. Economias adicionais foram feitas reduzindo o registro da pilha de 16 para 8 bits, o que significa que a pilha só poderia ter 256 bytes de comprimento, o que era suficiente para sua função pretendida de microcontrolador.

O registrador de índice IX de 16 bits foi dividido em dois, tornando-se X e Y. Mais importante, o estilo de acesso mudou; no 6800, o IX tinha um endereço de 16 bits, que era compensado por um número fornecido com a instrução, os dois foram adicionados para produzir o endereço final. No 6502 (e na maioria dos outros designs), o endereço base era armazenado na instrução e o X ou Y era adicionado a ele.

Por fim, o conjunto de instruções foi simplificado, liberando espaço no decodificador e na lógica de controle. Das 72 instruções originais no 6800, restaram 56. Entre os removidos estavam qualquer instrução que movesse dados entre os dois acumuladores do 6800, bem como várias instruções de desvio inspiradas no PDP-11, como a capacidade de comparar diretamente dois valores numéricos. O 6502 usava um sistema mais simples que tratava de comparações fazendo matemática no acumulador e examinando sinalizadores de resultado.

O design de alto nível do chip teve que ser transformado em desenhos de transistores e interconexões. Na MOS Technology, o "layout" era um processo muito manual feito com lápis de cor e papel pergaminho. O layout consistia em milhares de formas poligonais em seis desenhos diferentes; um para cada camada do processo de fabricação. Dados os limites de tamanho, todo o design do chip precisava ser constantemente considerado. Mensch e Paivinen trabalharam no decodificador de instrução enquanto Mensch, Peddle e Orgill trabalharam na ALU e nos registros. Outro avanço, desenvolvido em uma festa, foi uma maneira de compartilhar parte da fiação interna para permitir que a ALU fosse reduzida em tamanho.

Apesar de todos os esforços, o desenho final acabou ficando 5 mils a mais. Os primeiros 6502 chips tinham 168 × 183 mils (4,3 × 4,7 mm) ou uma área de 19,8 mm 2 . A instrução de rotação para a direita (ROR) não funcionou no primeiro silício, então a instrução foi temporariamente omitida dos documentos publicados, mas a próxima iteração do design encolheu o chip e corrigiu a instrução de rotação para a direita, que foi então incluída na documentação revisada .

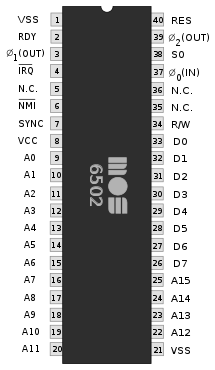

Apresentando o 6501 e o 6502

O MOS introduziria dois microprocessadores baseados no mesmo design subjacente: o 6501 seria conectado ao mesmo soquete do Motorola 6800, enquanto o 6502 reorganizaria a pinagem para suportar um oscilador de clock no chip. Ambos funcionariam com outros chips de suporte projetados para o 6800. Eles não executariam o software 6800 porque tinham um conjunto de instruções diferente, registros diferentes e, principalmente, modos de endereçamento diferentes. Rod Orgill foi responsável pelo design do 6501; ele ajudara John Buchanan na Motorola no 6800. Bill Mensch fez o 6502; ele foi o designer do 6820 Peripheral Interface Adapter (PIA) na Motorola. Harry Bawcom, Mike Janes e Sydney-Anne Holt ajudaram com o layout.

A introdução do microprocessador da MOS Technology foi diferente do lançamento do produto tradicional de meses. A primeira execução de um novo circuito integrado é normalmente usada para testes internos e compartilhada com clientes selecionados como "amostras de engenharia". Esses chips geralmente têm um ou dois pequenos defeitos de projeto que serão corrigidos antes do início da produção. O objetivo de Chuck Peddle era vender os primeiros chips 6501 e 6502 para os participantes da feira Wescon em San Francisco a partir de 16 de setembro de 1975. Peddle foi um porta-voz muito eficaz e os microprocessadores da MOS Technology foram amplamente cobertos pela imprensa especializada. Uma das primeiras foi uma história de página inteira sobre os microprocessadores MCS6501 e MCS6502 na edição de 24 de julho de 1975 da revista Electronics . As histórias também foram publicadas no EE Times (24 de agosto de 1975), EDN (20 de setembro de 1975), Electronic News (3 de novembro de 1975), Byte (novembro de 1975) e Microcomputer Digest (novembro de 1975). Anúncios do 6501 apareceram em várias publicações na primeira semana de agosto de 1975. O 6501 estaria à venda na Wescon por US $ 20 cada. Em setembro de 1975, os anúncios incluíam os microprocessadores 6501 e 6502. O 6502 custaria apenas $ 25 (equivalente a $ 120 em 2020).

Quando a MOS Technology chegou à Wescon, eles descobriram que os expositores não tinham permissão para vender nada no chão da exposição. Eles alugaram o MacArthur Suite no St. Francis Hotel e direcionaram os clientes de lá para comprar os processadores. Na suíte, os processadores eram armazenados em grandes potes para indicar que os chips estavam em produção e prontamente disponíveis. Os clientes não sabiam que a metade inferior de cada frasco continha chips não funcionais. Os chips custavam $ 20 e $ 25, enquanto o pacote de documentação custava $ 10 adicionais. Os usuários foram incentivados a fazer fotocópias dos documentos, uma forma barata de a MOS Technology distribuir informações sobre o produto. As folhas de dados preliminares listavam apenas 55 instruções, excluindo a instrução Rotate Right (ROR), que não funcionava corretamente nesses primeiros chips. As revisões em Byte e EDN observaram a falta da instrução ROR. A próxima revisão do layout corrigiu esse problema e a folha de dados de maio de 1976 listou 56 instruções. Peddle queria que todos os engenheiros e amadores interessados tivessem acesso aos chips e à documentação; outras empresas de semicondutores só queriam lidar com clientes "sérios". Por exemplo, a Signetics estava apresentando o microprocessador 2650 e seus anúncios pediam aos leitores que escrevessem informações no papel timbrado da empresa.

| Alfinete | 6800 | 6501 | 6502 |

|---|---|---|---|

| 2 | Halt | Preparar | Preparar |

| 3 | ∅1 (pol.) | ∅1 (pol.) | ∅1 (fora) |

| 5 | Endereço de memória válido | Endereço de memória válido | NC |

| 7 | Ônibus disponível | Ônibus disponível | SINCRONIZAR |

| 36 | Habilitar barramento de dados | Habilitar barramento de dados | NC |

| 37 | ∅2 (pol.) | ∅2 (pol.) | ∅0 (pol.) |

| 38 | NC | NC | Definir sinalizador de estouro |

| 39 | Controle de três estados | NC | ∅2 (fora) |

Ação da Motorola

A introdução do 6501/6502 na versão impressa e na Wescon foi um enorme sucesso. A desvantagem foi que a extensa cobertura da imprensa chamou a atenção da Motorola. Em outubro de 1975, a Motorola reduziu o preço de um único microprocessador 6800 de $ 175 para $ 69. O kit de design do sistema de $ 300 foi reduzido para $ 150 e agora vinha com uma placa de circuito impresso. Em 3 de novembro de 1975, a Motorola solicitou uma liminar na Justiça Federal para impedir a MOS Technology de fabricar e vender produtos de microprocessador. Eles também entraram com uma ação judicial alegando violação de patente e apropriação indébita de segredos comerciais. A Motorola afirmou que sete ex-funcionários se juntaram à MOS Technology para criar os produtos de microprocessador da empresa.

A Motorola era uma empresa de bilhões de dólares com um caso e advogados plausíveis. Em 30 de outubro de 1974, a Motorola entrou com vários pedidos de patente da família de microprocessadores e obteve 25 patentes. O primeiro foi em junho de 1976 e o segundo foi para Bill Mensch em 6 de julho de 1976, para o layout do chip 6820 PIA. Essas patentes cobriam o barramento 6800 e como os chips periféricos faziam interface com o microprocessador. A Motorola começou a fabricar transistores em 1950 e tinha um portfólio de patentes de semicondutores. A Allen-Bradley decidiu não lutar neste caso e vendeu sua participação na MOS Technology de volta aos fundadores. Quatro dos ex-engenheiros da Motorola foram nomeados no processo: Chuck Peddle, Will Mathys, Bill Mensch e Rod Orgill. Todos foram nomeados inventores nos 6800 pedidos de patentes. Durante o processo de descoberta, a Motorola descobriu que um engenheiro, Mike Janes, havia ignorado as instruções de Peddle e trouxe seus documentos de design 6800 para a MOS Technology. Em março de 1976, a agora independente MOS Technology estava ficando sem dinheiro e teve que resolver o caso. Eles concordaram em descartar o processador 6501, pagar à Motorola US $ 200.000 e devolver os documentos que a Motorola alegou serem confidenciais. Ambas as empresas concordaram em licenciar patentes de microprocessadores. Em maio daquele ano, a Motorola baixou o preço de um único microprocessador 6800 para US $ 35. Em novembro, a Commodore adquiriu a MOS Technology.

Computadores e jogos

Com problemas legais por trás deles, a MOS ainda tinha o problema de fazer os desenvolvedores experimentarem seu processador, o que levou Chuck Peddle a projetar o computador de placa única MDT-650 ("terminal de desenvolvimento de microcomputador") . Outro grupo dentro da empresa projetou o KIM-1 , que foi vendido semi-completo e poderia ser transformado em um sistema utilizável com a adição de um terminal de computador de terceiros e uma unidade de cassete compacta . Para sua surpresa, o KIM-1 vendeu bem para amadores e consertadores, bem como para os engenheiros aos quais foi destinado. O sistema de controle / treinamento / desenvolvimento Rockwell AIM 65 relacionado também foi bem. O software do AIM 65 foi baseado no MDT. Outro produto mais ou menos semelhante foi o Synertek SYM-1 .

Um dos primeiros usos "públicos" do design foi o microcomputador Apple I , lançado em 1976. O 6502 foi usado em seguida no Commodore PET e no Apple II , ambos lançados em 1977. Posteriormente, foi usado no Atari de 8 bits família e computadores domésticos Acorn Atom , o BBC Micro , Commodore VIC-20 e outros designs tanto para computadores domésticos quanto empresariais, como Ohio Scientific e Oric . O 6510 , um sucessor direto do 6502 com uma porta de E / S digital e um barramento de endereço de três estados , foi a CPU utilizada no computador doméstico Commodore 64 mais vendido . 6520 e / ou 6502-variantes CPUs foram usadas em todos do Commodore de disquetes unidades para todos os computadores de 8-bits, a partir da linha de PET (alguns dos quais tinha dois processadores baseados-6502) através da Commodore 128D, incluindo o Commodore64 , e em todas as unidades de disco da Atari para toda a sua linha de computadores de 8 bits, do 400/800 ao XEGS.

Outro uso importante da família 6500 foi em videogames. O primeiro a fazer uso do design do processador foi o Atari VCS, mais tarde renomeado para Atari 2600 . O VCS usava uma variante do 6502 chamada 6507 , que tinha menos pinos e, como resultado, podia endereçar apenas 8 KB de memória. Milhões de consoles Atari seriam vendidos, cada um com um processador MOS. Outro uso significativo foi pelo Nintendo Entertainment System e Famicom . O 6502 usado no NES era uma segunda versão de origem da Ricoh , um system-on-a-chip parcial , que não tinha o modo decimal com codificação binária , mas adicionou 22 registros mapeados em memória e hardware on-die para geração de som, leitura de joypad e DMA da lista de sprites . Chamado 2A03 em consoles NTSC e 2A07 em consoles PAL (a diferença é a proporção do divisor de memória e uma tabela de consulta para taxas de amostragem de áudio), este processador foi produzido exclusivamente para Nintendo . O Atari Lynx usou uma versão de 4 MHz do chip, o 65SC02 .

Na década de 1980, uma popular revista de eletrônicos Elektor / Elektuur usou o processador em sua placa de desenvolvimento de microprocessador Junior Computer .

- Computadores domésticos e consoles de videogame usando o 6502 ou suas variantes

Descrição técnica

| 1 5 | 1 4 | 1 3 | 1 2 | 1 1 | 1 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | (posição do bit) |

| Registros principais | ||||||||||||||||

| UMA | Um ccumulador | |||||||||||||||

| Registros de índice | ||||||||||||||||

| X | Índice X | |||||||||||||||

| Y | Índice Y | |||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | S | Ponteiro S tack | |||||||

| Contador de programa | ||||||||||||||||

| PC | P rogram C ounter | |||||||||||||||

| Registro de status | ||||||||||||||||

| N | V | - | B | D | eu | Z | C | P rocessor F desfasamentos | ||||||||

O 6502 é um processador little endian de 8 bits com um barramento de endereço de 16 bits . As versões originais foram fabricadas usando um chip de tecnologia de processo de 8 µm com um tamanho de matriz de 3,9 mm × 4,3 mm (anunciado como 153 mils × 168 mils ), para uma área total de 16,6 mm 2 .

A lógica interna funciona na mesma velocidade do clock externo, mas apesar das baixas velocidades de clock (normalmente em torno de 1 a 2 MHz ), o desempenho do 6502 era competitivo com outros CPUs contemporâneos usando clocks significativamente mais rápidos. Isso é parcialmente devido a uma máquina de estado simples implementada por lógica combinacional (sem relógio) em uma extensão maior do que em muitos outros projetos; o relógio de duas fases (fornecendo duas sincronizações por ciclo) poderia, portanto, controlar o ciclo da máquina diretamente. As instruções típicas podem levar metade dos ciclos para serem concluídas no 6502 do que em designs contemporâneos. Como a maioria das CPUs simples da época, o chip NMOS 6502 dinâmico não é sequenciado por um microcódigo ROM, mas usa um PLA (que ocupava cerca de 15% da área do chip) para decodificação e sequenciamento de instruções. Como na maioria dos microprocessadores de 8 bits, o chip faz alguma sobreposição limitada de busca e execução.

A baixa freqüência do clock moderou o requisito de velocidade da memória e periféricos acoplados ao CPU, já que apenas cerca de 50% do ciclo do clock estava disponível para acesso à memória (devido ao design assíncrono, esta fração variava fortemente entre as versões do chip). Isso foi crítico em um momento em que a memória acessível tinha tempos de acesso na faixa de 250–450 ns .

Como o chip só acessava a memória durante certas partes do ciclo do clock, e esses ciclos eram indicados pelo pino de baixa clock-out PHI2, outros chips em um sistema podiam acessar a memória durante os momentos em que o 6502 estava fora do barramento. Isso às vezes era conhecido como "acesso oculto". Essa técnica foi amplamente usada por sistemas de computador; eles usariam memória capaz de acessar a 2 MHz e, em seguida, executariam a CPU a 1 MHz. Isso garantiu que a CPU e o hardware de vídeo pudessem intercalar seus acessos, com um desempenho total igual ao do dispositivo de memória. Quando as memórias mais rápidas se tornaram disponíveis na década de 1980, as máquinas mais novas podiam funcionar com taxas de clock mais altas, como a CPU de 2 MHz na BBC Micro , e ainda usar as técnicas de compartilhamento de barramento.

Registros

Como seu precursor, o 6800, o 6502 tem poucos registros . Os registradores do 6502 incluem um registrador acumulador de 8 bits (A), dois registradores de índice de 8 bits (X e Y), 7 bits de sinalizador de status do processador de 1 bit (P) - especificamente do bit 7 ao bit 0 em P, estes são os negativo (N), estouro (V), reservado , quebra (B), decimal (D), desativação de interrupção (I), zero (Z) e sinalizador de transporte (C) -, um ponteiro de pilha de 8 bits (S), e um contador de programa de 16 bits (PC). Isso se compara a um design típico da mesma era, o Z80 , que tem oito registradores de 8 bits de uso geral, que podem ser combinados em quatro de 16 bits. O Z80 também tinha um conjunto completo de registradores alternativos, totalizando dezesseis registradores de uso geral.

Para compensar um pouco a falta de registros, o 6502 incluiu um modo de endereçamento de página zero que usa um byte de endereço na instrução em vez dos dois necessários para endereçar os 64 KB completos de memória. Isso fornece acesso rápido aos primeiros 256 bytes de RAM usando instruções mais curtas. Chuck Peddle disse em entrevistas que a intenção específica era permitir que esses primeiros 256 bytes de RAM fossem usados como registradores.

O espaço de endereço da pilha é conectado à página de memória $ 01 , ou seja, a faixa de endereço $ 0100 - $ 01FF ( 256 - 511 ). O acesso do software à pilha é feito por meio de quatro instruções de modo de endereçamento implícito, cujas funções são empurrar ou abrir (puxar) o acumulador ou o registrador de status do processador. A mesma pilha também é usada para chamadas de sub-rotina por meio das instruções JSR (salto para a sub-rotina) e RTS (retorno da sub-rotina) e para tratamento de interrupções .

Endereçando

O chip usa os registradores de índice e pilha efetivamente com vários modos de endereçamento , incluindo um modo rápido de "página direta" ou "página zero", semelhante ao encontrado no PDP-8 , que acessa locais de memória dos endereços de 0 a 255 com um único Endereço de 8 bits (salvando o ciclo normalmente necessário para buscar o byte de ordem superior do endereço) - o código para o 6502 usa a página zero da mesma forma que o código para outros processadores usaria registradores. Em alguns microcomputadores baseados em 6502 com um sistema operacional, o sistema operacional usa a maior parte da página zero, deixando apenas alguns locais para o usuário.

Os modos de endereçamento também incluem implícitos (instruções de 1 byte); absoluto (3 bytes); absoluto indexado (3 bytes); página zero indexada (2 bytes); relativo (2 bytes); acumulador (1); indirecta, x e indirecta, Y (2); e imediato (2). O modo absoluto é um modo de uso geral. As instruções de desvio usam um deslocamento de 8 bits assinado em relação à instrução após o desvio; o intervalo numérico -128..127, portanto, se traduz em 128 bytes para trás e 127 bytes para frente da instrução após o desvio (que é 126 bytes para trás e 129 bytes para frente desde o início da instrução de desvio). O modo de acumulador usa o acumulador como um endereço efetivo e não precisa de nenhum dado de operando . O modo imediato usa um operando literal de 8 bits .

Endereçamento indireto

Os modos indiretos são úteis para processamento de array e outros loops. Com o modo "(indireto), y" de ciclo 5/6, o registro Y de 8 bits é adicionado a um endereço base de 16 bits lido da página zero, que está localizado por um único byte após o opcode. O registro Y é, portanto, um registro de índice no sentido de que é usado para manter um índice real (ao contrário do registro X no 6800, onde um endereço de base era armazenado diretamente e ao qual um deslocamento imediato poderia ser adicionado). Incrementar o registrador de índice para percorrer o byte do array leva apenas dois ciclos adicionais. Com o modo menos freqüentemente usado "(indireto, x)", o endereço efetivo para a operação é encontrado no endereço da página zero formado pela adição do segundo byte da instrução ao conteúdo do registrador X. Usando os modos indexados, a página zero atua efetivamente como um conjunto de até 128 registradores de endereço adicionais (embora muito lentos).

O 6502 é capaz de realizar adição e subtração em binário ou decimal codificado em binário . Colocar a CPU no modo BCD com a SEDinstrução (definir sinalizador D) resulta em aritmética decimal, o que $99 + $01resultaria em $ 00 e o sinalizador carry (C) sendo definido. No modo binário ( CLD, limpar o sinalizador D), a mesma operação resultaria em $ 9A e o sinalizador de transporte sendo limpo. Além do Atari BASIC , o modo BCD raramente era usado em aplicativos de computador doméstico.

Veja o Hello world! artigo para um exemplo simples, mas característico da linguagem assembly 6502 .

Instruções e códigos de operação

Os códigos de operação da instrução 6502 ( opcodes ) têm oito bits de comprimento e têm a forma geral AAABBBCC, onde AAA e CC definem o opcode e BBB define o modo de endereçamento.

Por exemplo, considere a ORAinstrução, que realiza um OR bit a bit nos bits do acumulador com outro valor. O opcode de instrução tem o formato 000bbb01, onde bbb pode ser 010 para um valor de modo imediato (constante), 001 para endereço fixo de página zero, 011 para um endereço absoluto e assim por diante.

Esse padrão não é absoluto e há várias exceções. No entanto, onde se aplica, permite que se desconstrua facilmente os valores de opcode de volta para os mnemônicos de montagem para a maioria das instruções, lidando com os casos extremos com código de propósito especial.

Dos 256 códigos de operação possíveis disponíveis usando um padrão de 8 bits, o 6502 original usa 151 deles, organizados em 56 instruções com (possivelmente) modos de endereçamento múltiplos . Dependendo da instrução e do modo de endereçamento, o opcode pode exigir zero, um ou dois bytes adicionais para operandos. Conseqüentemente, as instruções da máquina 6502 variam em comprimento de um a três bytes. O operando é armazenado no formato little-endian habitual do 6502 .

O 65C816 , o descendente de CMOS de 16 bits do 6502, também suporta endereçamento de 24 bits, o que resulta em instruções sendo montadas com operandos de três bytes, também organizados no formato little-endian.

Os 105 opcodes restantes são indefinidos. No projeto original, as instruções em que os 4 bits de ordem inferior ( nibble ) eram 3, 7, B ou F não eram usadas, oferecendo espaço para expansão futura. Da mesma forma, a coluna $ 2x tinha apenas uma única entrada ,. Os 25 slots vazios restantes foram distribuídos. Alguns dos slots vazios foram usados no 65C02 para fornecer novas instruções, bem como variações das existentes com novos modos de endereçamento. As instruções $ Fx foram inicialmente deixadas livres para permitir que fornecedores terceiros adicionassem suas próprias instruções, mas versões posteriores do 65C02 padronizaram um conjunto de instruções de manipulação de bits desenvolvidas pela Rockwell Semiconductor .

LDX #constant

Linguagem de montagem

Uma instrução em linguagem assembly 6502 consiste em um mnemônico de instrução de três caracteres , seguido por quaisquer operandos . As instruções que não usam um operando separado, mas têm como alvo um único registro com base no modo de endereçamento, combinam o registro de destino no mnemônico de instrução, de modo que o montador usa INXao invés INC Xde incrementar o registro X.

Mesa de instrução

| Matriz de opcode para o conjunto de instruções 6502 | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Modos de endereçamento: A - acumulador, # - imediato, zpg - página zero, abs - absoluto, ind - indireto, X - indexado pelo registro X, Y - indexado pelo registro Y, rel - relativo | ||||||||||||

| Mordidela alta | Mordidela baixa | |||||||||||

| 0 | 1 | 2 | 4 | 5 | 6 | 8 | 9 | UMA | C | D | E | |

| 0 | BRK | ORA ( ind , X) | ORA zpg | ASL zpg | PHP | ORA # | ASL A | ORA abs | ASL abs | |||

| 1 | BPL rel | ORA ( ind ), Y | ORA zpg , X | ASL zpg , X | CLC | ORA abs , Y | ORA abs , X | ASL abs , X | ||||

| 2 | JSR abs | AND ( ind , X) | BIT zpg | E zpg | ROL zpg | PLP | E # | ROL A | BIT abs | E abs | ROL abs | |

| 3 | IMC rel | AND ( ind ), Y | E zpg , X | ROL zpg , X | SEC | E abs , Y | E abs , X | ROL abs , X | ||||

| 4 | RTI | EOR ( ind , X) | EOR zpg | LSR zpg | PHA | EOR # | LSR A | Abs JMP | EOR abs | LSR abs | ||

| 5 | BVC rel | EOR ( ind ), Y | EOR zpg , X | LSR zpg , X | CLI | EOR abs , Y | EOR abs , X | LSR abs , X | ||||

| 6 | RTS | ADC ( ind , X) | ADC zpg | ROR zpg | PLA | ADC # | ROR A | JMP ( ind ) | ADC abs | ROR abs | ||

| 7 | BVS rel | ADC ( ind ), Y | ADC zpg , X | ROR zpg , X | SEI | ADC abs , Y | ADC abs , X | ROR abs , X | ||||

| 8 | STA ( ind , X) | STY zpg | STA zpg | STX zpg | DEY | TXA | STY abs | STA abs | STX abs | |||

| 9 | BCC rel | STA ( ind ), Y | STY zpg , X | STA zpg , X | STX zpg , Y | TYA | STA abs , Y | TXS | STA abs , X | |||

| UMA | LDY # | LDA ( ind , X) | LDX # | LDY zpg | LDA zpg | LDX zpg | TAY | LDA # | TAX | LDY abs | LDA abs | LDX abs |

| B | BCS rel | LDA ( ind ), Y | LDY zpg , X | LDA zpg , X | LDX zpg , Y | CLV | LDA abs , Y | TSX | LDY abs , X | LDA abs , X | LDX abs , Y | |

| C | CPY # | CMP ( ind , X) | CPY zpg | CMP zpg | DEC zpg | INY | CMP # | DEX | CPY abs | Abs CMP | DEC abs | |

| D | BNE rel | CMP ( ind ), Y | CMP zpg , X | DEC zpg , X | CLD | CMP abs , Y | CMP abs , X | DEC abs , X | ||||

| E | CPX # | SBC ( ind , X) | CPX zpg | SBC zpg | INC zpg | INX | SBC # | NOP | CPX abs | SBC abs | INC abs | |

| F | BEQ rel | SBC ( ind ), Y | SBC zpg , X | INC zpg , X | SED | SBC abs , Y | SBC abs , X | INC abs , X | ||||

| Os opcodes em branco (por exemplo, F2 ) e todos os opcodes cujos nibbles baixos são 3 , 7 , B e F são indefinidos no conjunto de instruções 6502. | ||||||||||||

Comportamento detalhado

A entrada de interrupção não mascarável (NMI) do processador é sensível à borda , o que significa que a interrupção é disparada pela borda descendente do sinal em vez de seu nível. A implicação desse recurso é que um circuito de interrupção OR com fio não é prontamente suportado. No entanto, isso também evita que as interrupções NMI aninhadas ocorram até que o hardware torne a entrada NMI inativa novamente, geralmente sob o controle do manipulador de interrupções NMI .

A afirmação simultânea das linhas de interrupção de hardware NMI e IRQ (mascarável) faz com que o IRQ seja ignorado. No entanto, se a linha IRQ permanecer ativa após a manutenção do NMI, o processador responderá imediatamente ao IRQ, pois o IRQ é sensível ao nível . Assim, uma espécie de prioridade de interrupção embutida foi estabelecida no projeto 6502.

O sinalizador B é definido pelo 6502 amostrando periodicamente a saída do detector de borda NMI e sua entrada IRQ. O sinal de IRQ sendo direcionado para baixo só é reconhecido se os IRQs forem permitidos pelo sinalizador I. Se desta forma um pedido NMI ou IRQ (mascarável) for detectado, o sinalizador B é definido como zero e faz com que o processador execute a próxima instrução BRK em vez de executar a próxima instrução com base no contador do programa.

A instrução BRK então empurra o status do processador para a pilha, com o bit do sinalizador B definido como zero. No final de sua execução, a instrução BRK redefine o valor do sinalizador B para um. Esta é a única maneira pela qual o sinalizador B pode ser modificado. Se uma instrução diferente da instrução BRK colocar o sinalizador B na pilha como parte do status do processador, o sinalizador B sempre terá o valor um.

Uma borda de baixo para alto no pino de entrada SO definirá o bit de status de estouro do processador. Isso pode ser usado para uma resposta rápida ao hardware externo. Por exemplo, um driver de dispositivo de sondagem de alta velocidade pode sondar o hardware uma vez em apenas três ciclos usando uma BVCinstrução Branch-on-oVerflow-Clear ( ) que se ramifica até que o estouro seja definido por uma borda ascendente de SO. O Commodore 1541 e outras unidades de disquete Commodore usam essa técnica para detectar quando o serializador está pronto para transferir outro byte de dados do disco. O design de hardware e software do sistema deve garantir que um SO não ocorra durante o processamento aritmético e interrompa os cálculos.

Variações e derivados

Havia inúmeras variantes do NMOS 6502 original.

| Empresa | Modelo | Descrição |

|---|---|---|

| 6502A | Um chip de 1,5 MHz incluído no Asteroids Deluxe . | |

| 6502B | Versão do 6502 capaz de funcionar a uma velocidade máxima de 2 MHz em vez de 1. O B foi usado no Apple III , BBC Micro e, com clock de 1,79 MHz, nos primeiros computadores Atari de 8 bits . | |

| 6502C | O 6502C “oficial” era uma versão do 6502 original capaz de funcionar a até 4 MHz.

Não deve ser confundido com SALLY, um 6502 customizado projetado para Atari (e às vezes referido por eles como "6502C") nem com o 65C02 de nome semelhante . |

|

| SALLY / C014806 / "6502C" |

Variante 6502 personalizada projetada para Atari, usada em computadores Atari de 8 bits posteriores , bem como nos consoles Atari 5200 e Atari 7800 .

Apresenta um sinal HALT no pino 35 e o sinal R / W no pino 36 (esses pinos não estão conectados (N / C) em um 6502 padrão). Puxar HALT para baixo trava o relógio, pausando o processador. Isso foi usado para permitir o acesso direto à memória (DMA) do circuito de vídeo. Embora às vezes referido como "6502C" na documentação do Atari, não é o mesmo que o 6502C "oficial" e o chip em si nunca é marcado como tal. |

|

| Tecnologia MOS | 6503 | Capacidade de endereçamento de memória reduzida (4 KB) e nenhuma entrada RDY, em um pacote DIP de 28 pinos (com a fase 1 (OUT), SYNC, Vss redundante e pinos SO do 6502 também omitidos). |

| Tecnologia MOS | 6504 | Capacidade de endereçamento de memória reduzida (8 KB), sem NMI e sem entrada RDY, em um pacote DIP de 28 pinos (com a fase 1 (OUT), SYNC, Vss redundante e pinos SO do 6502 também omitidos). |

| Tecnologia MOS | 6505 | Capacidade de endereçamento de memória reduzida (4 KB) e sem NMI, em um pacote DIP de 28 pinos (com a fase 1 (OUT), SYNC, Vss redundante e pinos SO do 6502 também omitidos). |

| Tecnologia MOS | 6506 | Capacidade de endereçamento de memória reduzida (4 KB), sem NMI e sem entrada RDY, mas todos os 3 pinos de clock do 6502 (ou seja, um clock de saída de 2 fases), em um pacote DIP de 28 pinos (com o SYNC, Vss redundante, e os pinos SO do 6502 também omitidos). |

| Tecnologia MOS | 6507 | Capacidade de endereçamento de memória reduzida (8 KB) e sem interrupções, em um pacote DIP de 28 pinos (com a fase 1 (OUT), SYNC, Vss redundante e pinos SO do 6502 também omitidos). Este chip foi usado no sistema de videogame Atari 2600 . |

| Tecnologia MOS | 6508 | Possui uma porta de entrada / saída de 8 bits integrada e 256 bytes de RAM estática interna. |

| Tecnologia MOS | 6509 | Pode endereçar até 1 MB de RAM como 16 bancos de 64 KB e foi usado na série Commodore CBM-II . |

| Tecnologia MOS | 6510 | Possui uma porta de entrada / saída programável de 6 bits embutida e foi usado no Commodore 64 . O 8500 é efetivamente uma versão HMOS do 6510 e substituiu-o em versões posteriores do C64. |

| Tecnologia MOS |

6512 6513 6514 6515 |

A MOS Technology 6512, 6513, 6514 e 6515 dependem de um relógio externo, em vez de usar um gerador de relógio interno como o 650x (por exemplo, 6502). Isso foi usado com vantagem em alguns projetos em que os relógios podiam funcionar de forma assimétrica, aumentando o desempenho geral da CPU.

O 6512 é um 6502 com uma entrada de relógio de duas fases para um oscilador de relógio externo, em vez de um oscilador de relógio integrado. O 6513, 6514 e 6515 são similarmente equivalentes a (respectivamente) 6503, 6504 e 6505 com a mesma entrada de relógio de 2 fases. O 6512 foi usado no BBC Micro B + 64 . |

| Ricoh | 2A03 | Variante 6502 incluindo uma unidade de processamento de áudio e sem o modo BCD, usado no Nintendo Entertainment System . |

| Tecnologia MOS |

6591 6592 |

Projetos de sistema em um chip que utilizam um Atari 2600 completo em um pacote DIP de 48 pinos. |

| WDC | 65C02 |

Versão CMOS do NMOS 6502 que foi projetado por Bill Mensch do Western Design Center (WDC), apresentando consumo de energia reduzido, suporte para velocidades de clock muito maiores, novas instruções, novos modos de endereçamento para algumas instruções existentes e correção de erratas NMOS, como o JMP ($xxFF)bug.

|

| WDC | 65SC02 | Variante do WDC 65C02 sem operações de manipulação de bits individuais (RMB, SMB, BBR e BBS). Este núcleo, rodando a 4 MHz, foi usado no IC do sistema principal do Atari Lynx . |

| CSG (Tecnologia MOS) | 65CE02 | Derivado CMOS desenvolvido pelo Commodore Semiconductor Group (CSG), anteriormente MOS Technology. |

| Rockwell | R6511Q R6500 / 11, R6500 / 12, R6500 / 15 " Microcomputadores One-Chip " |

Versões aprimoradas do processador baseado em 6502, incluindo também operações de manipulação de bits individuais (RMB, SMB, BBR e BBS), RAM de página zero de 192 bytes no chip, UART , etc. |

| Rockwell | R65F11 R65F12 |

O Rockwell R65F11 (introduzido em 1983) e o posterior R65F12 são versões aprimoradas do processador baseado em 6502, incluindo também operações de manipulação de bits individuais (RMB, SMB, BBR e BBS), RAM de página zero no chip, no chip Forth ROM do kernel, um UART, etc. |

| GTE | G65SC102 | Software compatível com o 65C02, mas tem uma pinagem e circuito oscilador ligeiramente diferentes. O BBC Master Turbo incluiu a versão de 4 MHz deste CPU em uma placa de coprocessador, que também pode ser comprada separadamente e adicionada ao Master 128. |

| Rockwell | R65C00 R65C21 R65C29 |

O R65C00, R65C21 e R65C29 apresentavam dois CMOS 6502s aprimorados em um único chip, e o R65C00 e R65C21 continham adicionalmente 2 kB de ROM programável por máscara. |

| CM630 | Um clone do Bloco Oriental de 1 MHz do 6502 e foi usado no Pravetz 8A e 8C, clones búlgaros da série // da Apple . | |

| Tecnologia MOS |

7501 8501 |

Variantes do 6510 (ele mesmo um 6502 aprimorado), introduzido em 1984. Eles aumentaram o número de pinos de porta de E / S de 6 para 7, mas omitiram pinos para interrupção não mascarável e saída de clock. Usado nos computadores C-16 , C-116 e Plus / 4 do Commodore . A principal diferença entre as CPUs 7501 e 8501 é que a 7501 foi fabricada com o processo HMOS-1 e a 8501 com HMOS-2. |

| Tecnologia MOS | 8500 | Introduzido em 1985 como uma versão HMOS do 6510 (que por sua vez é baseado no 6502). Além da modificação do processo, o 8500 é virtualmente idêntico à versão NMOS do 6510. Ele substituiu o 6510 em versões posteriores do Commodore 64 . |

| Tecnologia MOS | 8502 | Projetado pela MOS Technology e usado no Commodore 128 . Baseado no MOS 6510 usado no Commodore 64, o 8502 foi capaz de rodar com o dobro do clock do 6510. A família 8502 também inclui o MOS 7501, 8500 e 8501. |

| Hudson Soft | HuC6280 | A versão aprimorada do WDC 65C02 da empresa japonesa de videogames Hudson Soft . Fabricado para eles pela Seiko Epson e NEC para o SuperGrafx . O produto mais notável que usa o HuC6280 é o console de videogame TurboGrafx-16 da NEC. |

Derivados de 16 bits

O Western Design Center projetou e atualmente produz o processador W65C816S , um sucessor de núcleo estático de 16 bits do 65C02 , com recursos bastante aprimorados. O W65C816S é uma variante mais recente do 65C816, que é o núcleo do computador Apple II GS e é a base do processador Ricoh 5A22 que alimenta o Super Nintendo Entertainment System . O W65C816S incorpora pequenas melhorias em relação ao 65C816 que tornam o chip mais recente não um substituto compatível com o hardware exato do anterior. Entre essas melhorias estava a conversão para um núcleo estático, o que torna possível parar o relógio em qualquer fase sem que os registradores percam dados. Disponível através de distribuidores de eletrônicos, a partir de março de 2020, o W65C816S é oficialmente classificado para operação em 14 MHz.

O Western Design Center também projetou e produziu o 65C802 , que era um núcleo 65C816 com um espaço de endereço de 64 kilobytes em um pacote compatível com o pino 65 (C) 02. O 65C802 poderia ser adaptado para uma placa 6502 e funcionaria como um 65C02 na inicialização, operando em "modo de emulação". Tal como acontece com o 65C816, uma sequência de duas instruções mudaria o 65C802 para a operação de "modo nativo", expondo seu acumulador de 16 bits e registradores de índice , bem como outros recursos aprimorados do 65C816. O 65C802 não foi amplamente utilizado; novos designs quase sempre foram construídos em torno do 65C816, resultando na interrupção da produção do 65C802.

Código de exemplo

O código-fonte da linguagem assembly 6502 a seguir é para uma sub-rotina chamada , que copia uma sequência de caracteres terminada em nulo de um local para outro, convertendo caracteres de letras maiúsculas em letras minúsculas. A string sendo copiada é a "fonte", e a string na qual a fonte convertida é armazenada é o "destino".

TOLOWER

0080

0080 00 04

0082 00 05

0600

0600 A0 00

0602 B1 80

0604 F0 11

0606 C9 41

0608 90 06

060A C9 5B

060C B0 02

060E 09 20

0610 91 82

0612 C8

0613 D0 ED

0615 38

0616 60

0617 91 82

0619 18

061A 60

061B

|

; TOLOWER:

;

; Convert a null-terminated character string to all lower case.

; Maximum string length is 255 characters, plus the null term-

; inator.

;

; Parameters:

;

; SRC - Source string address

; DST - Destination string address

;

ORG $0080

;

SRC .WORD $0400 ;source string pointer

DST .WORD $0500 ;destination string pointer

;

ORG $0600 ;execution start address

;

TOLOWER LDY #$00 ;starting index

;

LOOP LDA (SRC),Y ;get from source string

BEQ DONE ;end of string

;

CMP #'A' ;if lower than UC alphabet...

BCC SKIP ;copy unchanged

;

CMP #'Z'+1 ;if greater than UC alphabet...

BCS SKIP ;copy unchanged

;

ORA #%00100000 ;convert to lower case

;

SKIP STA (DST),Y ;store to destination string

INY ;bump index

BNE LOOP ;next character

;

; NOTE: If Y wraps the destination string will be left in an undefined

; state. We set carry to indicate this to the calling function.

;

SEC ;report string too long error &...

RTS ;return to caller

;

DONE STA (DST),Y ;terminate destination string

CLC ;report conversion completed &...

RTS ;return to caller

;

.END

|

Bugs e peculiaridades

O 6502 tinha vários bugs e peculiaridades, que tiveram que ser considerados ao programá-lo:

- As primeiras revisões do 6502, como aquelas enviadas com alguns computadores KIM-1 , tinham um bug grave na instrução ROR (girar a memória para a direita ou acumulador). A operação de ROR nesses chips é efetivamente uma instrução ASL (deslocamento aritmético para a esquerda) que não afeta o bit de transporte no registrador de status. O MOS deixou a instrução fora da documentação do chip inteiramente por causa do defeito, prometendo que ROR apareceria em 6502 chips a partir de 1976. A grande maioria dos 6502 chips existentes hoje não exibe esse bug.

- A família NMOS 6502 possui uma variedade de instruções não documentadas , que variam de um fabricante de chip para outro. A decodificação da instrução 6502 é implementada em uma matriz lógica com fio (semelhante a uma matriz lógica programável ) que é definida apenas para 151 dos 256 opcodes disponíveis . Os 105 restantes acionam ações estranhas e às vezes difíceis de prever, como travar o processador, executar duas instruções válidas consecutivamente, executar misturas estranhas de duas instruções ou simplesmente não fazer nada. A Eastern House Software desenvolveu o "Trap65", um dispositivo que é conectado entre o processador e seu soquete para converter (capturar) opcodes não implementados em instruções BRK (interrupção de software). Alguns programadores utilizaram esse recurso para estender o conjunto de instruções 6502, fornecendo funcionalidade para os opcodes não implementados com software especialmente escrito interceptado no vetor 0xFFFE da instrução BRK. Todos os opcodes indefinidos foram substituídos por instruções NOP no 65C02 , uma versão CMOS aprimorada do 6502, embora com tamanhos de byte e tempos de execução variáveis. No 65C802 / 65C816 , todos os 256 opcodes executam operações definidas.

- A instrução de salto indireto de memória do 6502

JMP (<address>), está parcialmente quebrada. Se <address> for hex xxFF (ou seja, qualquer palavra terminando em FF ), o processador não irá saltar para o endereço armazenado em xxFF exxFF+1como esperado, mas sim aquele definido por xxFF e xx00 (por exemplo,JMP ($10FF)iria saltar para o endereço armazenado em 10FF e 1000, em vez do armazenado em 10FF e 1100). Este defeito persistia em toda a linha NMOS, mas foi corrigido nos derivados CMOS. - O endereçamento indexado NMOS 6502 através dos limites da página fará uma leitura extra de um endereço inválido. Esta característica pode causar problemas aleatórios ao acessar hardware que atua em uma leitura, como limpar o temporizador ou sinalizadores de IRQ, enviar um handshake de E / S, etc. Este defeito continuou por toda a linha NMOS, mas foi corrigido nos derivados CMOS, em em que o processador faz uma leitura extra do último byte de instrução.

- As instruções de leitura-modificação-gravação do 6502 executam um ciclo de leitura e dois ciclos de gravação. Primeiro, os dados não modificados lidos são gravados de volta e, em seguida, os dados modificados são gravados. Essa característica pode causar problemas acessando duas vezes o hardware que atua em uma gravação. Esta anomalia continuou em toda a linha NMOS, mas foi corrigida nos derivados CMOS, nos quais o processador fará duas leituras e um ciclo de escrita. A prática de programação defensiva geralmente evitará esse problema, não executando instruções de leitura / modificação / gravação nos registros de hardware.

- Os sinalizadores de status N (resultado negativo), V (estouro de bit de sinal) e Z (resultado zero) geralmente não têm sentido ao realizar operações aritméticas enquanto o processador está no modo BCD , pois esses sinalizadores refletem o resultado binário, não BCD. Esta limitação foi removida nos derivados CMOS. Portanto, esse recurso pode ser usado para distinguir um processador CMOS de uma versão NMOS.

- Se o 6502 estiver no modo BCD quando ocorrer uma interrupção de hardware, ele não será revertido para o modo binário. Essa característica pode resultar em bugs obscuros na rotina de serviço de interrupção se ela falhar em limpar o modo BCD antes de realizar qualquer operação aritmética. Por exemplo, o Commodore 64 's KERNAL não lidar corretamente com essa característica processador, exigindo que IRQs ser desativado ou re-vectored durante operações matemáticas BCD. Este problema também foi abordado nos derivados CMOS.

- O conjunto de instruções 6502 inclui BRK (opcode $ 00), que é tecnicamente uma interrupção de software (semelhante em espírito ao mnemônico SWI dos processadores Motorola 6800 e ARM ). BRK é mais frequentemente usado para interromper a execução do programa e iniciar um monitor de linguagem de máquina para teste e depuração durante o desenvolvimento de software. O BRK também pode ser usado para rotear a execução do programa usando uma tabela de salto simples (semelhante à maneira como o Intel 8086 e seus derivados lidam com interrupções de software por número). No entanto, se ocorrer uma interrupção de hardware quando o processador estiver buscando uma instrução BRK, a versão NMOS do processador não conseguirá executar o BRK e, em vez disso, continuará como se apenas uma interrupção de hardware tivesse ocorrido. Esta falha foi corrigida na implementação CMOS do processador.

- Ao executar as instruções JSR (salto para a sub-rotina) e RTS (retorno da sub-rotina), o endereço de retorno enviado para a pilha por JSR é o do último byte do operando JSR (ou seja, o byte mais significativo do endereço da sub-rotina), em vez do endereço da instrução a seguir. Isso ocorre porque a cópia real (do contador do programa para a pilha e vice-versa) ocorre antes do incremento automático do contador do programa que ocorre no final de cada instrução. Esta característica passaria despercebida a menos que o código examinasse o endereço de retorno a fim de recuperar parâmetros no fluxo de código (um idioma de programação 6502 documentado no Manual de Referência Técnica ProDOS 8 ). Continua a ser uma característica de 6502 derivados até hoje.

Veja também

- Lista de 6502 montadores

- Computadores domésticos baseados em MOS Technology 6502

- Interrupções em processadores 65xx

- Contagem de transistores

- Aceleradores Apple II

- cc65 - 6502 macro assembler e C compilador

Notas

Referências

Citações

Bibliografia

- Peddle, Chuck (12 de junho de 2014). "História Oral de Chuck Peddle" (Entrevista). Entrevistado por Doug Fairbairn e Stephen Diamond.

- Bagnall, Brian (2010). Commodore, uma empresa no limite (2ª ed.). Winnipeg, Manitoba: Variant Press. ISBN 978-0-9738649-6-0.

- Bennett, Thomas; Ekiss, John; Lattin, William (Bill); Lavell, Jeff (28 de março de 2008). "Painel de História Oral Motorola 6800" (PDF) (Entrevista). Entrevistado por David Laws.

- Cushman, Robert H. (20 de setembro de 1975). "2-1 / 2 Generation μP's - $ 10 peças que funcionam como mini's low-end" (PDF) . EDN . Boston: Publicação Cahners. 20 (17): 36–42. Arquivado do original (PDF) em 24 de abril de 2016.

- Entrevista com William Mensch Stanford e o Projeto Vale do Silício, 9 de outubro de 1995. Transcrição

Leitura adicional

- Folhas de dados e manuais

- Folha de dados da série 6500 ; Tecnologia MOS; 12 páginas; 1976.

- Manual de Hardware da Série 6500 ; 2ª Ed; Tecnologia MOS; 182 páginas; 1976.

- Manual de programação da série 6500 ; 2ª Ed; Tecnologia MOS; 262 páginas; 1976.

- Livros

- 6502 Applications Book ; 1ª Ed; Rodnay Zaks ; Sybex; 281 páginas; 1979; ISBN 978-0895880154 . (arquivo)

- 6502 Assembly Language Programming ; 2ª Ed; Lance Leventhal; Osborne / McGraw-Hill; 650 páginas; 1986; ISBN 978-0078812163 . (arquivo)

- 6502 Subrotinas de linguagem assembly ; 1ª Ed; Lance Leventhal e Winthrop Saville; Osborne / McGraw-Hill; 550 páginas; 1982; ISBN 978-0931988592 . (arquivo)

- 6502 Games ; 1ª Ed; Rodnay Zaks; Sybex; 292 páginas; 1980; ISBN 978-0895880222 . (arquivo)

- 6502 Manual do usuário ; 1ª Ed; Joseph Carr; Reston; 288 páginas; 1984; ISBN 978-0835970020 . (arquivo)

- Programação 6502 avançada ; 1ª Ed; Rodnay Zaks; John Wiley & Sons; 292 páginas; 1982; ISBN 978-0895880895 . (arquivo)

- Linguagem de máquina para iniciantes - Programação de linguagem de máquina de computador pessoal para computadores Atari, VIC, Apple, C64 e PET ; 1ª Ed; Richard Mansfield; Calcular! Publicações; 350 páginas; 1983; ISBN 978-0942386110 . (arquivo)

- Programando o 6502 ; 4ª Ed; Rodnay Zaks; Sybex; 408 páginas; 1983; ISBN 978-0895881359 . (arquivo)

- Programando o 65816 - incluindo o 6502, 65C02 , 65802 ; 1ª Ed; David Eyes e Ron Lichty; Prentice Hall; 636 páginas; 1986; ISBN 978-0893037895 . (arquivo)

- Cartões de referência

- 6502 Cartão de referência instantânea do microprocessador ; James Lewis; Micro Logic; 2 páginas; 1980. (arquivo)

links externos

- 6502.org - o recurso do microprocessador 6502 - repositório

- The Rise of MOS Technology & The 6502 - Arquivo Commodore

- Informações 650x - descrição concisa, fotos de MOS e chips de segunda fonte; em cpu-collection.de

- mdfs.net - conjunto de instruções 6502

- Inteligente, Eric. "6502 - o primeiro RISC µP" . Arquivado do original em 24 de maio de 2012.

- Harrod, Dennette A. (outubro de 1980). "6502 obtém instruções microprogramáveis" . BYTE . Vol. 5 não. 10. McGraw Hill . pp. 282–285. ISSN 0360-5280 . Arquivado do original em 25/05/2006 . Página visitada em 14/05/2006 .

- Simuladores / emuladores

- Montador e emulador compatível com 6502 online, escrito em JavaScript Arquivado em 08/02/2011 na Wayback Machine

- Lista de 6502 emuladores de software - Domínio de Zophar

- Simulador 6502 para Windows - Atari Gaming Headquarters

- Simulação de nível de transistor visual de 6502 CPU

- MCL65 6502 CPU core - código C - MicroCore Labs GitHub

- Pranchas

- Placa 6502 de 7/8 chips de Grant

- Placa de treinamento do microprocessador 6502

- Construa sua própria placa de treinamento KIM-1 - consulte KIM-1

- 6502 computador doméstico

- PE6502 computador de placa única

- Computador de placa única BE6502 - baseado em vídeos Ben Eater

- FPGA

- cpu6502_tc 6502 CPU core - código-fonte VHDL - OpenCores

- ag_6502 6502 CPU core - código-fonte Verilog - OpenCores

- M65C02 65C02 CPU core - código fonte Verilog - OpenCores

- MCL65 6502 CPU core - Verilog - MicroCore Labs GitHub