POWER5 - POWER5

| Informação geral | |

|---|---|

| Lançado | 2004 |

| Projetado por | IBM |

| atuação | |

| Máx. Taxa de clock da CPU | 1,5 GHz a 2,3 GHz |

| Cache | |

| Cache L1 | 32 + 32 KB / núcleo |

| Cache L2 | 1.875 MB / chip |

| Cache L3 | 36 MB / chip (fora do chip) |

| Arquitetura e classificação | |

| Min. tamanho do recurso | 130 nm a 90 nm |

| Conjunto de instruções | PowerPC 2.02 |

| Especificações físicas | |

| Núcleos | |

| História | |

| Antecessor | POWER4 |

| Sucessor | POWER6 |

| Arquiteturas POWER , PowerPC e Power ISA |

|---|

| NXP (anteriormente Freescale e Motorola) |

| IBM |

|

| IBM / Nintendo |

| De outros |

| Links Relacionados |

| Cancelado em cinza , histórico em itálico |

O POWER5 é um microprocessador desenvolvido e fabricado pela IBM . É uma versão aprimorada do POWER4 . As principais melhorias são o suporte para multithreading simultâneo (SMT) e um controlador de memória no chip . O POWER5 é um microprocessador dual-core , com cada núcleo suportando um encadeamento físico e dois encadeamentos lógicos, para um total de dois encadeamentos físicos e quatro encadeamentos lógicos.

História

Os detalhes técnicos do microprocessador foram apresentados pela primeira vez na conferência de 2003 Hot Chips . Uma descrição mais completa foi fornecida no Microprocessor Forum 2003 em 14 de outubro de 2003. O POWER5 não era vendido abertamente e era usado exclusivamente pela IBM e seus parceiros. Os sistemas que utilizam o microprocessador foram introduzidos em 2004. O POWER5 competiu no mercado de servidores empresariais high-end, principalmente contra a Intel Itanium 2 e, em menor medida, a Sun Microsystems UltraSPARC IV ea Fujitsu SPARC64 V . Ele foi substituído em 2005 por uma iteração aprimorada, o POWER5 +.

Descrição

O POWER5 é um desenvolvimento adicional do POWER4 . A adição de multithreading bidirecional exigiu a duplicação da pilha de retorno, contador de programa , buffer de instrução, unidade de conclusão de grupo e fila de armazenamento para que cada thread pudesse ter o seu próprio. A maioria dos recursos, como os arquivos de registro e unidades de execução, são compartilhados, embora cada thread veja seu próprio conjunto de registros. O POWER5 implementa multithreading simultâneo (SMT), onde dois threads são executados simultaneamente. O POWER5 pode desativar o SMT para otimizar para a carga de trabalho atual.

Como muitos recursos, como os arquivos de registro, são compartilhados por dois encadeamentos, eles têm sua capacidade aumentada em muitos casos para compensar a perda de desempenho. O número de registradores inteiros e de ponto flutuante é aumentado para 120 cada, de 80 inteiros e 72 registradores de ponto flutuante no POWER4. O cache de instrução de ponto flutuante também teve sua capacidade aumentada de 20 para 24 entradas. A capacidade do cache unificado L2 foi aumentada para 1,875 MB e a associatividade do conjunto para 10 vias. O cache L3 unificado foi trazido na embalagem em vez de localizado externamente em chips separados. Sua capacidade foi aumentada para 36 MB. Como o POWER4, o cache é compartilhado pelos dois núcleos. O cache é acessado por meio de dois barramentos unidirecionais de 128 bits operando na metade da frequência do núcleo.

O controlador de memória on-die suporta até 64 GB de memória DDR e DDR2 . Ele usa barramentos seriais de alta frequência para se comunicar com buffers externos que fazem a interface dos módulos de memória em linha duplos (DIMMs) com o microprocessador.

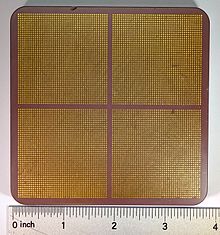

O POWER5 contém 276 milhões de transistores e possui uma área de 389 mm 2 . É fabricado pela IBM em um processo de 0,13 μm de silício sobre isolante (SOI) semicondutor de óxido de metal complementar (CMOS) com oito camadas de interconexão de cobre . A matriz POWER5 é embalada em um módulo de chip duplo (DCM) ou um módulo de multi-chip (MCM). O DCM contém um dado POWER5 e seu dado cache L3 associado. O MCM contém quatro matrizes POWER5 e quatro matrizes de cache L3, uma para cada matriz POWER5 e mede 95 mm por 95 mm.

Vários processadores POWER5 em sistemas high-end podem ser acoplados para atuar como um único processador vetorial por uma tecnologia chamada ViVA (Virtual Vector Architecture).

POWER5 +

O POWER5 + é uma iteração aprimorada do POWER5 apresentado em 4 de outubro de 2005. As melhorias inicialmente foram menor consumo de energia, devido ao processo mais recente em que foi fabricado. O chip POWER5 + usa um processo de fabricação de 90 nm. Isso resultou na diminuição do tamanho da matriz de 389 mm 2 para 243 mm 2 .

A frequência do relógio não foi aumentada no lançamento e permaneceu entre 1,5 e 1,9 GHz. Em 14 de fevereiro de 2006, novas versões aumentaram a frequência do clock para 2,2 GHz e depois para 2,3 GHz em 25 de julho de 2006.

O POWER5 + era empacotado nos mesmos pacotes dos microprocessadores POWER5 anteriores, mas também estava disponível em um módulo de quatro chips (QCM) contendo duas matrizes POWER5 + e duas matrizes de cache L3, uma para cada matriz POWER5 +. Esses chips QCM funcionam a uma frequência de clock entre 1,5 e 1,8 GHz.

Comercial

IBM utiliza os DCM e MCM microprocessadores POWER5 nas suas Sistema de p e i Sistema de famílias de servidores, na sua DS8000 servidor de armazenamento, e como microprocessadores embutidos na sua impressoras Infoprint alta-fim. Os microprocessadores DCM POWER5 são usados pela IBM em sua estação de trabalho IntelliStation POWER 285 de última geração . Os usuários terceirizados dos microprocessadores POWER5 são o Groupe Bull , em seus servidores Escala, e a Hitachi, em seus computadores SR11000 com até 128 microprocessadores POWER5 +, que possuem várias instalações incluídas na lista TOP500 de supercomputadores de 2007 . A IBM usa o POWER5 + QCM em seus servidores System p5 510Q, 520Q, 550Q e 560Q.

Notas

Veja também

Referências

- "IBM Previews Power5". (8 de setembro de 2003). Relatório do microprocessador .

- Clabes, Joachim et al. (2004). "Projeto e Implementação do Microprocessador POWER5". Proceedings of 2004 IEEE International Solid-State Circuits Conference .

- Glaskowsky, Peter N. (14 de outubro de 2003). "IBM Raises Curtain on Power5". Relatório do microprocessador .

- Kalla, Ron; Sinharoy, Balaram; Tendler, Joel M. (2004). "IBM Power5 Chip: Um processador Dual-Core Multithreaded". IEEE Micro .

- Krewell, Kevin (22 de dezembro de 2003). "Power5 Tops On Bandwidth". Relatório do microprocessador .

- Sinharoy, Balaram et al. (2005). "Microarquitetura do Sistema POWER5". IBM Journal of Research and Development .

- Vance, Ashlee (4 de outubro de 2005). "IBM bombeia linha Unix cheia de Power5 +" . The Register .

links externos

- Sizing up the Super Heavyweights , uma comparação e análise do POWER5 e Montecito, que explica as principais mudanças entre o POWER4 para o POWER5, juntamente com as estimativas de desempenho

- Um IBM Power5 + p5-575 Cluster 1600 e armazenamento DDN S2A9550 de alto desempenho , Texas A&M University