Memória de mudança de fase - Phase-change memory

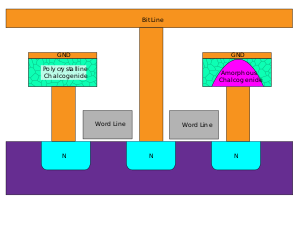

Memória de mudança de fase (também conhecido como PCM , PCME , PRAM , PCRAM , OUM ( memória unificada Ovonic ) e CRAM ou CRAM ( chalcogenide RAM )) é um tipo de memória de acesso aleatório não-volátil . Os PRAMs exploram o comportamento único do vidro calcogeneto . Na geração mais antiga do PCM, o calor produzido pela passagem de uma corrente elétrica através de um elemento de aquecimento geralmente feito de nitreto de titânio era usado para aquecer e extinguir rapidamente o vidro, tornando-o amorfo , ou para mantê-lo em sua faixa de temperatura de cristalização por algum tempo, mudando assim para um estado cristalino . O PCM também tem a capacidade de atingir uma série de estados intermediários distintos, tendo assim a capacidade de manter vários bits em uma única célula, mas as dificuldades em programar células dessa forma impediram que esses recursos fossem implementados em outras tecnologias (principalmente flash memória ) com a mesma capacidade.

A tecnologia PCM mais recente tem apresentado tendências em duas direções diferentes. Um grupo tem direcionado muitas pesquisas para a tentativa de encontrar alternativas materiais viáveis para Ge 2 Sb 2 Te 5 (GST), com sucesso misto. Outro grupo foi desenvolvido o uso de uma GETE-Sb 2 Te 3 superrede para alcançar alterações de fase não térmicos, simplesmente alterando o estado da coordenação dos átomos de germânio com um pulso de laser. Esta nova Memória de Mudança de Fase Interfacial (IPCM) teve muitos sucessos e continua a ser o local de muitas pesquisas ativas.

Leon Chua argumentou que todos os dispositivos de memória não volátil de dois terminais, incluindo PCM, deveriam ser considerados memristores . Stan Williams, do HP Labs , também argumentou que o PCM deveria ser considerado um memristor . No entanto, essa terminologia foi contestada e a aplicabilidade potencial da teoria do memristor a qualquer dispositivo fisicamente realizável está em aberto.

Fundo

Na década de 1960, Stanford R. Ovshinsky, da Energy Conversion Devices, explorou pela primeira vez as propriedades dos vidros de calcogeneto como uma potencial tecnologia de memória. Em 1969, Charles Sie publicou uma dissertação, na Iowa State University, que descreveu e demonstrou a viabilidade de um dispositivo de memória de mudança de fase integrando um filme de calcogeneto a um arranjo de diodos . Um estudo cinematográfico em 1970 estabeleceu que o mecanismo de memória de mudança de fase no vidro de calcogeneto envolve o crescimento de filamentos cristalinos induzido por campo elétrico. Na edição de setembro de 1970 da Electronics , Gordon Moore , cofundador da Intel , publicou um artigo sobre a tecnologia. No entanto, problemas de qualidade do material e consumo de energia impediram a comercialização da tecnologia. Mais recentemente, o interesse e a pesquisa foram retomados, já que as tecnologias de memória flash e DRAM devem encontrar dificuldades de dimensionamento à medida que a litografia do chip diminui.

Os estados cristalino e amorfo do vidro calcogeneto têm valores de resistividade elétrica dramaticamente diferentes . O estado amorfo de alta resistência representa um binário 0, enquanto o estado cristalino de baixa resistência representa 1. O calcogeneto é o mesmo material usado em mídia óptica regravável (como CD-RW e DVD-RW ). Nesses casos, as propriedades ópticas do material são manipuladas, ao invés de sua resistividade elétrica, visto que o índice de refração do calcogeneto também muda com o estado do material.

Embora o PRAM ainda não tenha alcançado o estágio de comercialização para dispositivos eletrônicos de consumo, quase todos os dispositivos protótipos fazem uso de uma liga de calcogeneto de germânio , antimônio e telúrio ( GeSbTe ) chamada GST. A estequiometria ou razão do elemento Ge: Sb: Te é 2: 2: 5. Quando o GST é aquecido a uma temperatura alta (acima de 600 ° C), sua cristalinidade de calcogeneto é perdida. Uma vez resfriado, ele é congelado em um estado de vidro amorfo e sua resistência elétrica é alta. Ao aquecer o calcogeneto a uma temperatura acima de seu ponto de cristalização , mas abaixo do ponto de fusão , ele se transformará em um estado cristalino com uma resistência muito menor. O tempo para completar esta transição de fase depende da temperatura. As porções mais frias do calcogeneto demoram mais para cristalizar e as porções superaquecidas podem ser fundidas novamente. Uma escala de tempo de cristalização da ordem de 100 ns é comumente usada. Isso é mais longo do que os dispositivos convencionais de memória volátil, como a DRAM moderna , que tem um tempo de comutação da ordem de dois nanossegundos. No entanto, um pedido de patente da Samsung Electronics em janeiro de 2006 indica que o PRAM pode atingir tempos de comutação de até cinco nanossegundos.

Um avanço mais recente lançado pela Intel e ST Microelectronics permite que o estado do material seja controlado com mais cuidado, permitindo que ele seja transformado em um dos quatro estados distintos; os estados amorfos ou cristalinos anteriores, junto com dois novos estados parcialmente cristalinos. Cada um desses estados tem diferentes propriedades elétricas que podem ser medidas durante as leituras, permitindo que uma única célula represente dois bits, dobrando a densidade da memória.

PRAM vs. Flash

O tempo de comutação do PRAM e a escalabilidade inerente o tornam mais atraente. A sensibilidade à temperatura do PRAM é talvez sua desvantagem mais notável, que pode exigir mudanças no processo de produção dos fabricantes que incorporam a tecnologia.

A memória flash funciona modulando a carga ( elétrons ) armazenada na porta de um transistor MOS . O portão é construído com uma "pilha" especial projetada para reter cargas (em um portão flutuante ou em "armadilhas" isolantes ). A presença de carga dentro da porta muda a tensão de limiar do transistor , para cima ou para baixo, correspondendo a 1 para 0, por exemplo. Alterar o estado do bit requer a remoção da carga acumulada, o que exige uma voltagem relativamente grande para "sugar" os elétrons da porta flutuante. Essa explosão de tensão é fornecida por uma bomba de carga , que leva algum tempo para acumular energia. Os tempos gerais de gravação para dispositivos Flash comuns são da ordem de 100 μs (para um bloco de dados), cerca de 10.000 vezes o tempo de leitura típico de 10 ns, para SRAM, por exemplo (para um byte).

O PRAM pode oferecer um desempenho muito maior em aplicativos em que escrever rapidamente é importante, porque o elemento de memória pode ser alternado mais rapidamente e também porque bits únicos podem ser alterados para 1 ou 0 sem a necessidade de primeiro apagar um bloco inteiro de células. O alto desempenho do PRAM, milhares de vezes mais rápido do que os discos rígidos convencionais, o torna particularmente interessante em funções de memória não volátil que atualmente têm desempenho limitado pelo tempo de acesso à memória.

Além disso, com o Flash, cada explosão de voltagem na célula causa degradação. À medida que o tamanho das células diminui, os danos da programação pioram porque a voltagem necessária para programar o dispositivo não se ajusta à litografia. A maioria dos dispositivos flash é classificada, atualmente, para apenas 5.000 gravações por setor, e muitos controladores flash realizam nivelamento de desgaste para espalhar as gravações em muitos setores físicos.

Os dispositivos PRAM também se degradam com o uso, por motivos diferentes dos do Flash, mas se degradam muito mais lentamente. Um dispositivo PRAM pode suportar cerca de 100 milhões de ciclos de gravação. A vida útil do PRAM é limitada por mecanismos como degradação devido à expansão térmica do GST durante a programação, migração de metal (e outro material) e outros mecanismos ainda desconhecidos.

As peças do flash podem ser programadas antes de serem soldadas a uma placa ou mesmo adquiridas pré-programadas. O conteúdo de um PRAM, no entanto, é perdido devido às altas temperaturas necessárias para soldar o dispositivo a uma placa (consulte soldagem por refluxo ou soldagem por onda ). Isso é agravado pela recente tendência à fabricação sem chumbo, que exige temperaturas de soldagem mais altas. O fabricante que usa peças PRAM deve fornecer um mecanismo para programar a PRAM "no sistema" depois de ter sido soldada no lugar.

As portas especiais usadas na memória Flash "vazam" carga (elétrons) ao longo do tempo, causando corrupção e perda de dados. A resistividade do elemento de memória em PRAM é mais estável; na temperatura normal de trabalho de 85 ° C, projeta-se que retenha os dados por 300 anos.

Modulando cuidadosamente a quantidade de carga armazenada na porta, os dispositivos Flash podem armazenar vários (geralmente dois) bits em cada célula física. Na verdade, isso dobra a densidade da memória, reduzindo o custo. Dispositivos PRAM originalmente armazenavam apenas um único bit em cada célula, mas os avanços recentes da Intel eliminaram esse problema.

Como os dispositivos Flash prendem elétrons para armazenar informações, eles são suscetíveis à corrupção de dados por radiação, tornando-os inadequados para muitas aplicações espaciais e militares. PRAM exibe maior resistência à radiação.

Os seletores de células PRAM podem usar vários dispositivos: diodos , BJTs e MOSFETs . Usar um diodo ou um BJT fornece a maior quantidade de corrente para um determinado tamanho de célula. No entanto, a preocupação com o uso de diodo decorre de correntes parasitas para células vizinhas, bem como de uma maior exigência de tensão, resultando em maior consumo de energia. Sendo a resistência do calcogeneto uma resistência necessariamente maior do que o diodo, a tensão de operação deve exceder 1 V por uma ampla margem para garantir a corrente de polarização direta adequada do diodo. Talvez a consequência mais severa do uso de uma matriz selecionada por diodo, em particular para grandes matrizes, seja a corrente de fuga de polarização reversa total das linhas de bits não selecionadas. Em matrizes selecionadas por transistor, apenas as linhas de bits selecionadas contribuem com a corrente de fuga de polarização reversa. A diferença na corrente de fuga é de várias ordens de magnitude. Uma outra preocupação com a escala abaixo de 40 nm é o efeito de dopantes discretos conforme a largura da junção pn diminui. Os seletores baseados em filme fino permitem densidades mais altas, utilizando área de célula <4 F 2 ao empilhar camadas de memória horizontal ou verticalmente. Freqüentemente, os recursos de isolamento são inferiores ao uso de transistores se a relação liga / desliga do seletor não for suficiente, limitando a capacidade de operar matrizes muito grandes nesta arquitetura. O interruptor de limite baseado em calcogeneto foi demonstrado como um seletor viável para matrizes de PCM de alta densidade

2000 e mais tarde

Em agosto de 2004, a Nanochip licenciou a tecnologia PRAM para uso em dispositivos de armazenamento de sondas MEMS (sistemas microelétricos -mecânicos). Esses dispositivos não são de estado sólido. Em vez disso, uma bandeja muito pequena revestida de calcogeneto é arrastada por baixo de muitas (milhares ou até milhões) de sondas elétricas que podem ler e gravar o calcogeneto. A tecnologia de micro-mover da Hewlett-Packard pode posicionar com precisão o prato em 3 nm, de forma que densidades de mais de 1 Tbit (125 GB) por polegada quadrada sejam possíveis se a tecnologia puder ser aperfeiçoada. A ideia básica é reduzir a quantidade de fiação necessária no chip; em vez de conectar cada célula, as células são colocadas mais próximas umas das outras e lidas pela corrente que passa pelas sondas MEMS, agindo como fios. Essa abordagem se parece muito com a tecnologia Millipede da IBM .

Célula Samsung 46,7 nm

Em setembro de 2006, a Samsung anunciou um protótipo de dispositivo de 512 Mb (64 MB) usando interruptores de diodo. O anúncio foi uma surpresa e foi especialmente notável por sua densidade bastante alta. O protótipo apresentava um tamanho de célula de apenas 46,7 nm, menor do que os dispositivos Flash comerciais disponíveis na época. Embora dispositivos Flash de maior capacidade estivessem disponíveis (64 Gb, ou 8 GB, estavam chegando ao mercado), outras tecnologias competindo para substituir o Flash em geral ofereciam densidades mais baixas (tamanhos de células maiores). Os únicos dispositivos MRAM e FeRAM de produção têm apenas 4 Mb, por exemplo. A alta densidade do protótipo do dispositivo PRAM da Samsung sugeria que ele poderia ser um competidor de Flash viável, e não limitado a funções de nicho como outros dispositivos têm sido. O PRAM parecia ser particularmente atraente como um substituto potencial para o Flash NOR, onde as capacidades dos dispositivos normalmente ficam atrás das dos dispositivos Flash NAND . (As capacidades de última geração em NAND ultrapassaram 512 Mb há algum tempo.) NOR Flash oferece densidades semelhantes ao protótipo PRAM da Samsung e já oferece endereçamento de bits (ao contrário de NAND, onde a memória é acessada em bancos de muitos bytes por vez).

Dispositivo PRAM da Intel

O anúncio da Samsung foi seguido por outro da Intel e da STMicroelectronics , que demonstraram seus próprios dispositivos PRAM no Intel Developer Forum de 2006 em outubro. Eles mostraram uma peça de 128 Mb que começou a ser fabricada no laboratório de pesquisa da STMicroelectronics em Agrate, Itália. A Intel afirmou que os dispositivos eram estritamente à prova de conceito.

Dispositivo BAE

PRAM também é uma tecnologia promissora nas indústrias militar e aeroespacial, onde os efeitos da radiação tornam o uso de memórias não voláteis padrão, como o Flash, impraticável. Os dispositivos de memória PRAM foram introduzidos pela BAE Systems , conhecidos como C-RAM, alegando excelente tolerância à radiação ( rad-hard ) e imunidade de travamento . Além disso, a BAE reivindica uma duração do ciclo de gravação de 10 8 , o que permitirá que ela seja uma candidata à substituição de PROMs e EEPROMs em sistemas espaciais.

Célula multinível

Em fevereiro de 2008, a Intel e a STMicroelectronics revelaram o primeiro protótipo de matriz PRAM multinível ( MLC ). O protótipo armazenava dois bits lógicos em cada célula física, na verdade 256 Mb de memória armazenados em uma matriz física de 128 Mb. Isso significa que, em vez dos dois estados normais - totalmente amorfo e totalmente cristalino -, dois estados intermediários distintos adicionais representam diferentes graus de cristalização parcial, permitindo que o dobro de bits sejam armazenados na mesma área física. Em junho de 2011, a IBM anunciou que havia criado uma memória de mudança de fase de vários bits estável, confiável, com alto desempenho e estabilidade.

Dispositivo de 90 nm da Intel

Também em fevereiro de 2008, a Intel e a STMicroelectronics enviaram amostras de protótipos de seu primeiro produto PRAM para os clientes. O produto de 90 nm, 128 Mb (16 MB) foi denominado Alverstone.

Em junho de 2009, a Samsung e a Numonyx BV anunciaram um esforço colaborativo no desenvolvimento de produtos de hardware feitos sob medida para o mercado PRAM.

Em abril de 2010, a Numonyx anunciou a linha Omneo de memórias de mudança de fase compatíveis com NOR de 128 Mbit. A Samsung anunciou o envio de 512 Mb de RAM de mudança de fase (PRAM) em um pacote de vários chips (MCP) para uso em aparelhos móveis até o outono de 2010.

Alumínio / antimônio

Dispositivos de memória de mudança de fase baseados em germânio, antimônio e telúrio apresentam desafios de fabricação, uma vez que o ataque químico e o polimento do material com calcogênios podem alterar a composição do material. Materiais baseados em Al e Sb são mais estáveis termicamente do que Ge-Sb-Te. Al 50 Sb 50 tem três níveis de resistência distintos, oferecendo o potencial para armazenar três bits de dados em duas células em vez de dois (nove estados possíveis para o par de células, usando oito desses estados resulta log 2 8 = 3 bits).

Desafios

O maior desafio para a memória de mudança de fase tem sido a exigência de alta densidade de corrente de programação (> 10 7 A / cm², em comparação com 10 5 ... 10 6 A / cm² para um transistor ou diodo típico). O contato entre a região de mudança de fase quente e o dielétrico adjacente é outra preocupação fundamental. O dielétrico pode começar a vazar corrente em temperatura mais alta ou pode perder adesão ao expandir a uma taxa diferente do material de mudança de fase.

A memória de mudança de fase é suscetível a uma troca fundamental de mudança de fase não intencional versus pretendida. Isso decorre principalmente do fato de que a mudança de fase é um processo controlado termicamente, em vez de um processo eletrônico. As condições térmicas que permitem a cristalização rápida não devem ser muito semelhantes às condições de espera, por exemplo, temperatura ambiente. Caso contrário, a retenção de dados não pode ser sustentada. Com a energia de ativação adequada para a cristalização, é possível ter uma cristalização rápida em condições de programação, enquanto uma cristalização muito lenta em condições normais.

Provavelmente, o maior desafio para a memória de mudança de fase é sua resistência de longo prazo e desvio de tensão de limiar. A resistência do estado amorfo aumenta lentamente de acordo com uma lei de potência (~ t 0,1 ). Isso limita severamente a capacidade de operação multinível (um estado intermediário inferior seria confundido com um estado intermediário superior posteriormente) e também poderia prejudicar a operação padrão de dois estados se a tensão limite aumentar além do valor do projeto.

Em abril de 2010, a Numonyx lançou sua linha Omneo de chips PRAM de substituição de flash NOR de 128 Mb de interface paralela e serial . Embora os chips de flash NOR que eles pretendiam substituir operassem na faixa de −40 ... 85 ° C, os chips PRAM operavam na faixa de 0 ... 70 ° C, indicando uma janela de operação menor em comparação com o flash NOR. Isso provavelmente se deve ao uso de junções p-n altamente sensíveis à temperatura para fornecer as altas correntes necessárias para a programação.

Linha do tempo

- Janeiro de 1955 : Kolomiets e Gorunova revelaram propriedades semicondutoras de vidros de calcogeneto .

- Setembro de 1966 : Stanford Ovshinsky registra a primeira patente sobre tecnologia de mudança de fase

- Janeiro de 1969 : Charles H. Sie publicou uma dissertação na Iowa State University sobre dispositivo de memória de mudança de fase de calcogeneto

- Junho de 1969 : Patente dos EUA 3.448.302 (Shanefield) licenciada para Ovshinsky reivindica a primeira operação confiável do dispositivo PRAM

- Setembro de 1970 : Gordon Moore publica pesquisas na Electronics Magazine

- Junho de 1999 : A joint venture Ovonyx é formada para comercializar a tecnologia PRAM

- Novembro de 1999 : Lockheed Martin trabalha com Ovonyx em PRAM para aplicações espaciais

- Fevereiro de 2000 : Intel investe no Ovonyx, licencia tecnologia

- Dezembro de 2000 : ST Microelectronics licencia a tecnologia PRAM da Ovonyx

- Março de 2002 : Macronix registra um pedido de patente para PRAM sem transistor

- Julho de 2003 : Samsung começa a trabalhar na tecnologia PRAM

- 2003 a 2005 : pedidos de patente relacionados a PRAM apresentados por Toshiba, Hitachi, Macronix, Renesas, Elpida, Sony, Matsushita, Mitsubishi, Infineon e mais

- Agosto de 2004 : Nanochip licencia a tecnologia PRAM da Ovonyx para uso em armazenamento de sonda MEMS

- Agosto de 2004 : Samsung anuncia matriz PRAM de 64 Mbit de sucesso

- Fevereiro de 2005 : Elpida licencia a tecnologia PRAM da Ovonyx

- Setembro de 2005 : a Samsung anuncia uma matriz PRAM de 256 Mbit de sucesso, anuncia uma corrente de programação de 400 μA

- Outubro de 2005 : Intel aumenta investimento no Ovonyx

- Dezembro de 2005 ; Hitachi e Renesas anunciam PRAM de 1,5 V com corrente de programação de 100 μA

- Dezembro de 2005 : Samsung licencia a tecnologia PRAM da Ovonyx

- Julho de 2006 : BAE Systems começa a vender o primeiro chip PRAM comercial

- Setembro de 2006 : Samsung anuncia dispositivo PRAM de 512 Mbit

- Outubro de 2006 : Intel e STMicroelectronics mostram um chip PRAM de 128 Mbit

- Dezembro de 2006 : IBM Research Labs demonstra um protótipo de 3 por 20 nanômetros

- Janeiro de 2007 : Qimonda licencia a tecnologia PRAM da Ovonyx

- Abril de 2007 : O diretor de tecnologia da Intel, Justin Rattner, fará a primeira demonstração pública da tecnologia PRAM (phase-change RAM) da empresa

- Outubro de 2007 : Hynix começa a buscar PRAM licenciando a tecnologia da Ovonyx

- Fevereiro de 2008 : Intel e STMicroelectronics anunciam MLC PRAM de quatro estados e começam a enviar amostras aos clientes.

- Dezembro de 2008 : A Numonyx anuncia a produção em massa do dispositivo PRAM de 128 Mbit para um cliente selecionado.

- Junho de 2009 : a mudança de fase da RAM da Samsung entrará em produção em massa a partir de junho

- Setembro de 2009 : Samsung anuncia o início da produção em massa de dispositivo PRAM de 512 Mbit

- Outubro de 2009 : Intel e Numonyx anunciam que encontraram uma maneira de empilhar matrizes de memória de mudança de fase em um dado

- Dezembro de 2009 : Numonyx anuncia produto de 1 Gb 45 nm

- Abril de 2010 : Numonyx lança Omneo PRAM Series (P8P e P5Q), ambos em 90 nm.

- Abril de 2010 : Samsung lança PRAM de 512 Mbits com processo de 65 nm, em Multi-Chip-Package.

- Fevereiro de 2011 : a Samsung apresentou PRAM de 58 nm 1,8 V 1 Gb.

- Fevereiro de 2012 : Samsung apresentou PRAM de 20 nm 1,8 V 8 Gb

- Julho de 2012 : Micron anuncia a disponibilidade de Phase-Change Memory para dispositivos móveis - a primeira solução PRAM em produção de volume

- Janeiro de 2014 : a Micron retira todas as peças de PCM do mercado.

- Maio de 2014 : IBM demonstra a combinação de PCM, NAND convencional e DRAM em um único controlador

- Agosto de 2014 : Western Digital demonstra armazenamento de protótipo de PCM com 3 milhões de E / S e latência de 1,5 microssegundo

- Julho de 2015 : A Intel e a Micron anunciaram a memória 3D Xpoint, onde a liga de mudança de fase é usada como parte de armazenamento de uma célula de memória.

Veja também

- RAM Ferroelétrica (FRAM)

- Memória magnetorresistiva de acesso aleatório (MRAM)

- Memória principalmente de leitura (RMM)

Referências

links externos

- Mícron

- Ovonyx, Inc.

- Dispositivos de conversão de energia, Inc.

- PRAM Hitachi / Renesas de baixo consumo

- Armazenamento de sonda Hewlett-Packard

- Simpósio Europeu \ Phase Change and Ovonics

- Comunicado de imprensa da NVM endurecida por radiação BAE C-RAM

- Folha de dados do NVM endurecido por radiação BAE C-RAM

- Introdução ao PCM da Numonyx (vídeo)