Codificador de prioridade - Priority encoder

Um codificador de prioridade é um circuito ou algoritmo que compacta várias entradas binárias em um número menor de saídas. A saída de um codificador de prioridade é a representação binária do número original começando do zero do bit de entrada mais significativo. Eles são freqüentemente usados para controlar solicitações de interrupção agindo na entrada de interrupção de prioridade mais alta.

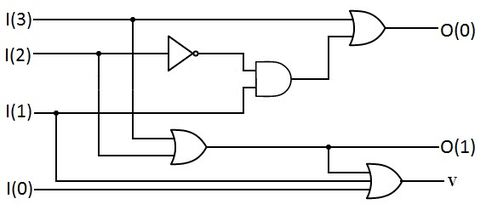

Se duas ou mais entradas forem fornecidas ao mesmo tempo, a entrada com a prioridade mais alta terá precedência . Um exemplo de um único codificador de bit 4 a 2 é mostrado, onde as entradas de prioridade mais alta estão à esquerda e "x" indica um valor irrelevante - ou seja, qualquer valor de entrada produz a mesma saída, pois é substituído pela entrada de prioridade mais alta. A saída V indica se a entrada é válida.

| I 3 | I 2 | Eu 1 | I 0 | O 1 | O 0 | V |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | x | x | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | x | 0 | 1 | 1 |

| 0 | 1 | x | x | 1 | 0 | 1 |

| 1 | x | x | x | 1 | 1 | 1 |

Codificadores de prioridade podem ser facilmente conectados em matrizes para fazer codificadores maiores, como um codificador de 16 para 4 feito de seis codificadores de prioridade 4 para 2 - quatro codificadores de 4 para 2 com a fonte de sinal conectada às suas entradas, e os dois codificadores restantes recebem a saída dos quatro primeiros como entrada. O codificador de prioridade é uma melhoria em um circuito codificador simples, em termos de lidar com todas as configurações de entrada possíveis .

Construção recursiva de codificadores prioritários

Um codificador de prioridade, também chamado de detector de zero à esquerda (LZD) ou contador de zero à esquerda (LZC), recebe um vetor de entrada de bits e detecta o índice do primeiro binário '1' no vetor de entrada. Um sinal válido indica se algum binário '1' foi detectado no vetor de entrada, portanto, o índice é válido.

Os codificadores de prioridade podem ser construídos de forma eficiente por recursão. O vetor de entrada é dividido em fragmentos iguais com bits. Um codificador de prioridade com largura mais estreita de 𝑛 / 𝑘 é aplicado para cada fragmento. O bit válido de cada um dos vai para um bit para detectar o primeiro fragmento válido. A localização desse fragmento é a parte superior do índice geral e orienta a localização exata dentro do próprio fragmento para produzir a parte inferior do índice geral.

A profundidade da estrutura proposta é , enquanto a complexidade da área de hardware é . Se o Stratix V da Altera ou dispositivo equivalente for usado, é recomendado obter maior desempenho e compressão de área, uma vez que o mux pode ser implementado usando 6-LUT, portanto, um ALM completo.

Um gerador Verilog de código aberto para o codificador de prioridade recursiva está disponível online.

Uma descrição comportamental do codificador de prioridade em Verilog é a seguinte.

// behavioural description of priority enconder;

// https://github.com/AmeerAbdelhadi/Indirectly-Indexed-2D-Binary-Content-Addressable-Memory-BCAM

module pe_bhv

#( parameter OHW = 512 ) // encoder one-hot input width

( input clk , // clock for pipelined priority encoder

input rst , // registers reset for pipelined priority encoder

input [ OHW -1:0] oht , // one-hot input / [ OHW -1:0]

output reg [`log2(OHW)-1:0] bin , // first '1' index/ [`log2(OHW)-1:0]

output reg vld ); // binary is valid if one was found

// use while loop for non fixed loop length

// synthesizable well with Intel's QuartusII

always @(*) begin

bin = {`log2(OHW){1'b0}};

vld = oht[bin] ;

while ((!vld) && (bin!=(OHW-1))) begin

bin = bin + 1 ;

vld = oht[bin];

end

end

endmodule

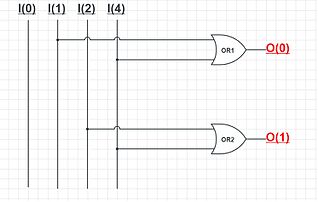

Codificador simples

Um circuito codificador simples é um conversor one-hot para binário. Ou seja, se houver 2 n linhas de entrada, e no máximo apenas uma delas será alta, o código binário desta linha 'ativa' é produzido nas linhas de saída de n bits.