Escada do resistor - Resistor ladder

Uma escada de resistores é um circuito elétrico feito de unidades repetidas de resistores . Duas configurações são discutidas abaixo, uma escada de resistor de string e uma escada R-2R.

Uma escada R – 2R é uma maneira simples e barata de realizar a conversão digital para analógico , usando arranjos repetitivos de redes de resistores precisas em uma configuração semelhante a uma escada . Uma escada de resistor de string implementa a rede de referência não repetitiva.

Rede de escada de resistor de string (conversão analógica para digital ou ADC)

Uma sequência de muitos resistores, muitas vezes igualmente dimensionados, conectados entre duas tensões de referência é uma rede em escada de sequência de resistores. Os resistores atuam como divisores de tensão entre as tensões referenciadas. Cada tap do string gera uma tensão diferente, que pode ser comparada com outra tensão : este é o princípio básico de um ADC (conversor analógico-digital) flash . Freqüentemente, uma tensão é convertida em corrente , possibilitando o uso de uma rede ladder R – 2R.

- Desvantagem: para um ADC de n bits, o número de resistores cresce exponencialmente , pois os resistores são necessários, enquanto a escada de resistores R – 2R aumenta apenas linearmente com o número de bits, pois precisa apenas de resistores.

- Vantagem: valores de impedância mais altos podem ser alcançados usando o mesmo número de componentes.

Rede de escada de resistor R – 2R (conversão de digital para analógico)

Uma rede básica em escada de resistor R – 2R é mostrada na Figura 1. Bit a n -1 (bit mais significativo, MSB) até o bit a 0 (bit menos significativo, LSB) são acionados a partir de portas lógicas digitais. Idealmente, as entradas de bits são comutadas entre V = 0 (lógica 0) e V = V ref (lógica 1). A rede R – 2R faz com que esses bits digitais sejam ponderados em sua contribuição para a tensão de saída V out . Dependendo de quais bits são definidos para 1 e quais para 0, a tensão de saída ( V saída ) terá um valor escalonado correspondente entre 0 e V ref menos o valor do passo mínimo, correspondendo ao bit 0. O valor real de V ref (e a tensão da lógica 0) dependerá do tipo de tecnologia usada para gerar os sinais digitais.

Para um valor digital VAL, de um R – 2R DAC com N bits e níveis lógicos de referência 0 V / V , a tensão de saída V out é:

Por exemplo, se N = 5 (portanto, 2 N = 32) e V ref = 3,3 V (tensão lógica CMOS típica 1), então V out irá variar entre 0 volts (VAL = 0 = 00000 2 ) e o máximo (VAL = 31 = 11111 2 ):

com etapas (correspondendo a VAL = 1 = 00001 2 )

A escada R – 2R é barata e relativamente fácil de fabricar, uma vez que apenas dois valores de resistor são necessários (ou mesmo um, se R for feito colocando um par de 2R em paralelo, ou se 2R for feito colocando um par de R em Series). É rápido e tem impedância de saída R fixa. A escada R – 2R opera como uma sequência de divisores de corrente , cuja precisão de saída depende exclusivamente de quão bem cada resistor é correspondido com os outros. Pequenas imprecisões nos resistores MSB podem sobrecarregar inteiramente a contribuição dos resistores LSB. Isso pode resultar em um comportamento não monotônico em cruzamentos importantes, como de 01111 2 a 10000 2 . Dependendo do tipo de portas lógicas usadas e do projeto dos circuitos lógicos, pode haver picos de tensão de transição em cruzamentos importantes, mesmo com valores de resistor perfeitos. Eles podem ser filtrados com capacitância no nó de saída (a redução consequente na largura de banda pode ser significativa em algumas aplicações). Finalmente, a resistência 2R está em série com a impedância de saída digital. Portas de alta impedância de saída (por exemplo, LVDS ) podem ser inadequadas em alguns casos. Por todas as razões acima (e sem dúvida outras), esse tipo de DAC tende a ser restrito a um número relativamente pequeno de bits; embora os circuitos integrados possam aumentar o número de bits para 14 ou até mais, 8 bits ou menos é o mais comum.

Precisão de escadas de resistor R – 2R

Os resistores usados com os bits mais significativos devem ser proporcionalmente mais precisos do que aqueles usados com os bits menos significativos; por exemplo, na rede R – 2R discutida acima, as imprecisões nos resistores bit-4 (MSB) devem ser insignificantes em comparação com R / 32 (ou seja, muito melhores do que 3%). Além disso, para evitar problemas na transição 10000 2 -para-01111 2 , a soma das imprecisões nos bits inferiores deve ser significativamente menor do que R / 32. A precisão necessária dobra a cada bit adicional: para 8 bits, a precisão necessária será melhor do que 1/256 (0,4%). Dentro de circuitos integrados , redes R – 2R de alta precisão podem ser impressas diretamente em um único substrato usando tecnologia de filme fino , garantindo que os resistores compartilhem características elétricas semelhantes . Mesmo assim, muitas vezes eles devem ser cortados a laser para atingir a precisão necessária. Essas escadas de resistores no chip para conversores digital para analógico que alcançam a precisão de 16 bits foram demonstradas. Em uma placa de circuito impresso, usando componentes discretos, resistores de 1% de precisão seriam suficientes para um circuito de 5 bits; no entanto, com contagens de bits além disso, o custo de resistores de precisão cada vez maiores torna-se proibitivo. Para um conversor de 10 bits, mesmo usando resistores de precisão de 0,1% não garantem a monotonicidade da saída. Dito isso, as escadas R-2R de alta resolução formadas por componentes discretos às vezes são usadas, a não linearidade sendo corrigida no software. Um exemplo de tal abordagem pode ser visto na fonte de alimentação Korad 3005.

Escada de resistor com degraus desiguais

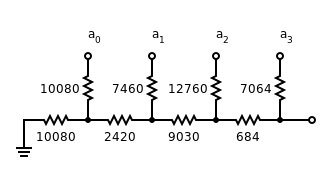

Não é necessário que cada "degrau" da escada R – 2R use os mesmos valores de resistor. É apenas necessário que o valor "2R" corresponda à soma do valor "R" mais a resistência equivalente a Thévenin dos degraus de menor importância. A Figura 2 mostra um DAC linear de 4 bits com resistores desiguais.

Isso permite que um DAC razoavelmente preciso seja criado a partir de uma coleção heterogênea de resistores, formando o DAC um bit por vez. Em cada estágio, os resistores para a "linha" e "perna" são escolhidos de forma que o valor da linha corresponda ao valor da perna mais a resistência equivalente dos degraus anteriores. Os resistores de degrau e perna podem ser formados pelo emparelhamento de outros resistores em série ou paralelo para aumentar o número de combinações disponíveis. Este processo pode ser automatizado.

Veja também

Referências

links externos

- ECE209: Notas de aula do DAC - Ohio State University

- EE247: Conversores D / A - Berkeley University of California

- Notas de aula simplificadas do DAC / ADC - Universidade de Michigan

- Conversores digital para analógico (slides) - Georgia Tech

- Tutorial MT-014: String DACs e DACs Totalmente Decodificados - Dispositivos Analógicos

- Tutorial MT-015: DACs Binários - Dispositivos Analógicos

- Tutorial MT-016: DACs segmentados - Dispositivos analógicos

- Tutorial MT-018: DACs intencionalmente não lineares - Dispositivos analógicos

- R2R Resistor Ladder Networks - BI Technologies

- Nota de aplicação de redes Ladder R / 2R - TT Electronics