Texas Instruments TMS9900 - Texas Instruments TMS9900

| Designer | Instrumentos Texas |

|---|---|

| Bits | 16 bits |

| Introduzido | 1976 |

| Projeto | CISC |

| Endianness | Grande |

| Registros | |

| PC, WP, ST | |

| Propósito geral | 2 localizados internamente no processador (WP, ST) pilha de 16 × 16 bits localizada na RAM externa |

Introduzido em junho de 1976, o TMS9900 foi um dos primeiros microprocessadores de 16 bits de chip único disponíveis comercialmente . É implementado Texas Instruments ' TI-990 minicomputador arquitetura em um formato de chip único, e foi inicialmente usado para modelos low-end de que lineup.

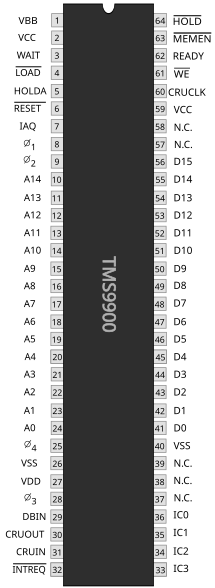

Seu formato DIP de 64 pinos tornou-o mais caro para implementar em máquinas menores do que o formato mais comum de 40 pinos, e viu relativamente poucos ganhos de design fora do uso da própria TI. Entre esses usos estava o computador doméstico TI-99/4 da TI , que vendeu cerca de 2,8 milhões de exemplares.

Em meados da década de 1980, o campo do microcomputador estava mudando para sistemas de 16 bits, como o Intel 8088, e designs de 16/32 bits mais recentes, como o Motorola 68000 , que superavam facilmente o 9900 e eram geralmente mais baratos. Sem um futuro óbvio para o chip, a TI voltou sua atenção para processadores para fins especiais, como o Texas Instruments TMS320 , lançado em 1983.

História

O TMS9900 foi projetado como uma versão de chip único da série de minicomputadores TI 990 , assim como o Intersil 6100 era um chip único PDP-8 (12 bits), e o Fairchild 9440 e Data General mN601 eram versões de um chip do Data General de Nova . Ao contrário dos microprocessadores de 16 bits com vários chips, como o National Semiconductor IMP-16 ou DEC LSI-11 , alguns dos quais anteriores ao TMS9900, o último era um microprocessador de 16 bits autônomo de um único chip. O único design de 16 bits de chip único conhecido que precede o TMS9900 é o quase desconhecido Panafacom MN1610 , lançado em 1975.

As raízes do minicomputador do TMS9900 dão origem a uma série de características arquitetônicas que não são comumente encontradas em projetos que começaram a partir de uma folha em branco. Notável entre eles foi o uso do TMS9900 de registradores que são mapeados na memória principal . Isso permite a troca rápida de contexto , que pode ser realizada alterando um único ponteiro, ao passo que projetos mais tradicionais exigiriam que todo o conjunto de registros internos fosse armazenado na memória ou na pilha. A desvantagem dessa abordagem é que o acesso a esses registros consome mais tempo. Em uma implementação de minicomputador, o efeito é relativamente pequeno e a vantagem em um ambiente multitarefa é significativa. Em outras funções, como microcomputadores de usuário único ou sistemas embarcados, essa compensação pode não valer a pena.

A TI usou a mesma arquitetura em diferentes divisões para obter sinergia corporativa: "uma empresa, uma arquitetura de computador". No final dos anos 1970, Walden C. Rhines fez uma apresentação do TMS9900 para um grupo da IBM que desenvolvia um computador pessoal. "Não saberíamos até 1981 o que havíamos perdido" porque a IBM escolheu o Intel 8088 para o IBM PC , ele lembrou. Após a tentativa fracassada de entrar no mercado de computadores pessoais com produtos como o TI-99 / 4A , a divisão de microprocessadores da empresa finalmente mudou o foco para a série de processadores para fins especiais TMS320 .

Arquitetura

O TMS9900 tem três registros internos de 16 bits - contador de programa (PC), registro de status (ST) e registro de ponteiro de espaço de trabalho (WP). O registro WP aponta para um endereço base na RAM externa onde os 16 registros de usuário de propósito geral do processador (cada um com 16 bits de largura) são mantidos. Essa arquitetura permite a troca rápida de contexto ; por exemplo, quando uma sub - rotina é inserida, apenas o registro do espaço de trabalho único precisa ser alterado, em vez de exigir que os registros sejam salvos individualmente.

Os endereços referem-se a bytes com a convenção de ordenação big endian . O TMS9900 é uma máquina clássica de 16 bits com um espaço de endereço de 2 16 bytes (65.536 bytes ou 32.768 palavras).

Não há conceito de pilha e nenhum registro de ponteiro de pilha. Em vez disso, existem instruções de desvio que salvam o contador do programa em um registro e alteram o contexto do registro. Os 16 vetores de interrupção de hardware e 16 de software consistem, cada um, em um par de valores de PC e WP, de modo que a troca de contexto de registro também é realizada automaticamente por uma interrupção.

Conjunto de instruções e endereçamento

O TMS9900 tem 69 instruções com uma, duas ou três palavras e sempre alinhadas por palavra na memória. O conjunto de instruções é razoavelmente ortogonal , o que significa que, com poucas exceções, as instruções podem usar todos os métodos de acesso a operandos (modos de endereçamento).

Os modos de endereçamento incluem Imediato (operando na instrução), Direto ou "Simbólico" (endereço do operando na instrução), Registro (operando no registro do espaço de trabalho), Registro Indireto (endereço do operando no registro do espaço de trabalho) com ou sem incremento automático, Indexado (endereço do operando na instrução indexada com o conteúdo do registro do espaço de trabalho) e Relativo do contador do programa.

As instruções de operando duplo mais importantes (adicionar, subtrair, comparar, mover etc.) contêm modo de endereçamento de 2 bits e campos de seletor de registro de 4 bits para operandos de origem e destino. No opcode, o modo "Simbólico" é representado como modo Indexado com o campo de registro definido como 0, portanto, o registro de espaço de trabalho 0 (WR0) não pode ser usado no modo Indexado. Em instruções de operando duplo usadas com menos frequência, como XOR, o operando de destino deve ser um registro de área de trabalho (ou par de registros de área de trabalho no caso de instruções de multiplicação e divisão).

O controle de fluxo é facilitado por um grupo de uma instrução de salto incondicional e doze instruções de salto condicionais. Os alvos de salto são relativos ao PC com um deslocamento de endereços de -128 a +127 palavras.

Para chamadas de sub-rotina, a instrução Branch and Load Workspace Pointer (BLWP) carrega novos valores de WP e PC, então salva os valores de WP, PC e ST para os (novos) registros 13, 14 e 15 respectivamente. No final da sub-rotina, o Return Workspace Pointer (RTWP) os restaura na ordem inversa. Usando BLWP / RTWP, é possível aninhar chamadas de sub-rotina, apesar da ausência de uma pilha, no entanto, o programador precisa atribuir o espaço de trabalho de registro apropriado explicitamente.

O conjunto de instruções também contém um opcode Branch and Link (BL) que salva apenas o PC no registrador 11 sem alterar o WP. Nesse caso, uma instrução de desvio (B) usando WR11 como endereço de destino pode servir como opcode de retorno, mas as sub-rotinas do tipo BL não podem ser aninhadas sem que o programador execute ações para salvar o endereço de retorno.

O TMS9900 suporta uma instrução de execução "X" (eXecute). Esta instrução executa a instrução em um registrador. Ele pode ser usado para depuração (como uma instrução de ponto de interrupção ) e para criar tabelas de código de operação indexadas como usadas em interpretadores de código de byte.

O TMS9900 também oferece suporte à instrução eXtended OPeration (XOP). O XOP recebe um número no intervalo de 0 a 15, bem como um endereço de origem. Quando chamada, a instrução executará uma troca de contexto por meio de um dos dezesseis vetores em locais predefinidos na memória. Isso é semelhante a uma interrupção, mas a instrução XOP também armazena o endereço de origem no registro 11 da nova área de trabalho. O XOP é menos flexível que o BLWP, pois os vetores de transferência têm que estar em locais fixos, mas economiza memória, já que o endereço de origem pode ser usado pela sub-rotina executada, quando não está definindo a localização do vetor. O XOP é usado para implementar instruções no software em modelos de extremidade inferior, onde versões de extremidade superior da série de minicomputadores 990 podem ter hardware dedicado para executá-las.

Em comparações típicas com o Intel 8086 , o TMS9900 tinha programas menores. As únicas desvantagens eram o pequeno espaço de endereço e a necessidade de RAM rápida.

Implementação

O TMS9900 foi implementado em um processo MOS de porta de silício de canal N, que exigia fontes de alimentação de +5 V, −5 V e +12 V e um clock de quatro fases (sem sobreposição) com uma frequência máxima de 3 MHz (333 ns ciclo), geralmente gerado a partir de um cristal de 48 MHz usando um chip gerador de clock TIM9904 (também conhecido como 74LS362).

As instruções mais curtas requerem oito ciclos de clock ou 2,7 μs para serem concluídas (assumindo 0 ciclos de espera externos), muitas outras funcionam entre 10 e 14 ciclos (3,3 ... 4,7 μs); a instrução de execução mais longa (DIV) pode levar até 124 ciclos (41,3 μs).

O chip foi empacotado em um (então incomum) DIP de 64 pinos, 0,9 "de largura . O número comparativamente grande de pinos permitiu que o barramento de endereço de 15 bits (palavra) e o barramento de dados de 16 bits fossem colocados em pinos dedicados sem o uso de multiplexação (ao contrário, por exemplo, da CPU Intel 8086 ), mantendo as conexões de memória externa simples. Ao contrário da convenção usada por muitos outros fabricantes, a TI rotulou o endereço mais significativo e as linhas de dados "A0" e "D0", respectivamente. Todos internos os caminhos de dados e a ALU têm 16 bits de largura.

O processador pode ser pausado com o barramento de endereço tri-declarado para acesso direto à memória externa (DMA). Os acessos à memória têm sempre 16 bits de largura, com a CPU realizando automaticamente operações de leitura antes de gravar para acessos de todo o byte.

O sistema de interrupção de hardware suporta uma entrada de prioridade de interrupção de 4 bits, que precisava ser mais alta do que o nível de prioridade armazenado no registrador de status (bits 12-15) para que a solicitação de interrupção fosse atendida. Além disso, a entrada / LOAD fornece um recurso de interrupção não mascarável com um vetor dedicado.

A CPU TMS9900 também contém um registrador de deslocamento de 16 bits ("CRU") projetado para fazer interface com registradores de deslocamento externos, com instruções dedicadas que dão suporte ao acesso a campos de largura de 1 a 16 bits de um total de 4096 bits endereçáveis.

Os periféricos paralelos podem ser conectados de forma mapeada na memória ao endereço regular e ao barramento de dados.

Formulários

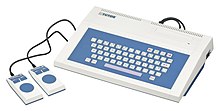

O TMS9900 foi usado nos computadores domésticos TI-99/4 e TI-99 / 4A . Infelizmente, para reduzir os custos de produção, a TI optou por usar nesses sistemas apenas 128 palavras de 16 bits do tipo rápido de RAM que o TMS9900 poderia acessar diretamente. O resto da memória foi 16kB de 8 bits DRAM que era acessível apenas indirectamente através do controlador de monitor de vídeo, o que prejudicou a performance da TI-99/4.

A TI desenvolveu a série TM990 de módulos de computador, incluindo CPU, memória e E / S, que, quando conectados a um quadro de cartão, podem formar um minicomputador de 16 bits. Eles eram normalmente usados para controle de processo. Um treinador de microprocessador foi lançado no formato TM990 / 189.

Desenvolvimento de produtos da família TMS9900

A segunda geração da família TMS9900 de microprocessadores foi o TMS9995, que forneceu "desempenho funcional em velocidades 3 vezes mais rápidas do que qualquer processador da família 9900 anterior", em grande parte devido à inclusão da tecnologia de pré-busca de instruções. Na área de computadores domésticos, o TMS9995 só encontrou uso no Tomy Tutor , em uma atualização esotérica do TI99-4 / A chamada Geneve 9640 e em um projeto impresso na Electronics Today : o Powertran Cortex. Ele foi planejado para ser usado nos sistemas de computador TI-99/2 e TI-99/8, mas nenhum avançou além do estágio de protótipo.

Posteriormente, a TI desenvolveu a família de microprocessadores TMS99000 mais poderosa, que foi usada como CPU no minicomputador 990 / 10A como uma redução de custo. Infelizmente, quando o 990 / 10A chegou ao mercado, o fim da era dos minicomputadores já estava à vista.

A família TMS99000 inclui dois microprocessadores, o TMS99105A e o TMS99110A, que são idênticos, exceto pela inclusão de memória ROM de macrostore no chip (a memória de macrostore contém funções adicionais ou instruções por meio de rotinas de emulação escritas em código de máquina padrão). O Macrostore ROM no chip no microprocessador TMS99110A contém instruções de ponto flutuante que estão disponíveis como parte do conjunto de instruções em linguagem de máquina, enquanto o TMS99105A não inclui um macrostore ROM. Um terceiro membro da família TMS99000, o TMS99120, foi anunciado, mas pode nunca ter sido produzido comercialmente. O ROM Macrostore no chip no TMS99120 contém rotinas de suporte em tempo de execução para a linguagem de alto nível PASCAL.

O conjunto de instruções para a família TMS99000 é um superconjunto do TMS9995 e TMS9900, com compatibilidade de código de objeto. As instruções adicionais incluem aquelas para multiplicação e divisão assinadas; mudar, adicionar e subtrair palavras longas; registro de status de carga, ponteiro de local de trabalho de carga, operações de pilha, suporte a multiprocessador, manipulação de bits. Os membros da família podem acessar instantaneamente 256 KiB de memória e podem usar o mapeador de memória TIM99610 para endereçar até 16 MiB. A arquitetura contém muitos outros avanços em relação ao TMS9900 e TMS9995.

Variantes

| Modelo | Descrição |

|---|---|

| TI990 / 9 | Primeira CPU multi-chip para sistemas de minicomputador, 1974 |

| TI990 / 10 | Implementação de multi-chip para sistemas de minicomputador, 1975 |

| TI990 / 12 | Implementação de vários chips, mais rápido do que 990/10 |

| TMS9900 | Implementação de chip único, 1976, usado no computador TI-99/4 (A) |

| TMS9940 | Microcontrolador com 2KB ROM, 128B RAM, decrementador, barramento CRU, 1979 |

| TMS9980 TMS9981 |

Versões de 8 bits do TMS9900 |

| TMS9985 | TMS9940 com 8KB ROM, 256B RAM e um barramento externo de 8 bits, c. 1978 (nunca lançado) |

| TMS9989 | 9980 aprimorado, usado em hardware militar |

| TMS9995 | Aprimorado tipo TMS9985, sem ROM. Usado nos protótipos TI-99/2 e TI-99/8, o Tomy Tutor e o computador Geneve |

| TMS99105 | Membro da linha de base da família de microprocessadores TMS99000 |

| TMS99110 | Microprocessador da família TMS99000 com instruções de ponto flutuante pré-programadas na memória ROM Macrostore on-chip |

| TMS99120 | Microprocessador da família TMS99000 com rotinas de suporte em tempo de execução para a linguagem de alto nível PASCAL pré-programada na memória ROM Macrostore on-chip (o microprocessador foi anunciado, mas pode nunca ter sido produzido comercialmente) |

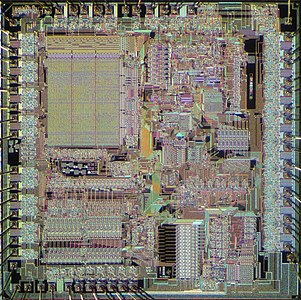

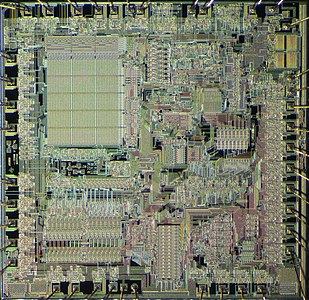

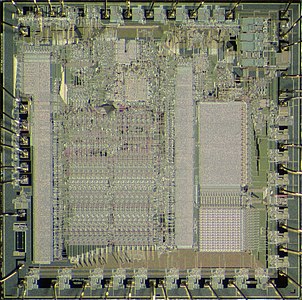

- Morrer fotos

Referências

links externos

- Manuais TMS9900 e referências da Bitsavers