NEC V20 - NEC V20

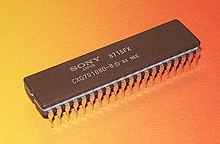

NEC V20 (µPD70108), 8 MHz

| |

| Informação geral | |

|---|---|

| Lançado | Março de 1984 |

| Fabricante (s) comum (is) | |

| atuação | |

| Largura de dados | 16 bits |

| Especificações físicas | |

| Transistores | |

| Núcleos | |

| Coprocessador | |

O NEC V20 era um microprocessador feito pela NEC . Era tanto o pino quanto o código-objeto compatível com o Intel 8088 , com um conjunto de instruções semelhante ao do Intel 80188 com algumas extensões. O V20 foi lançado em março de 1984.

Recursos

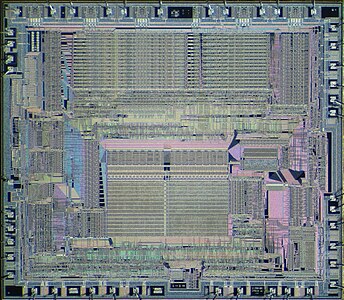

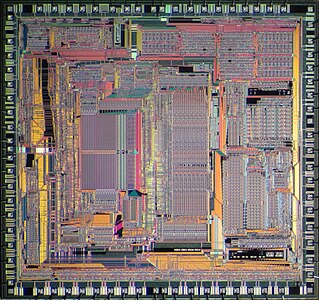

O dado do V20 compreendia 63.000 transistores , mais do que o dobro dos 29.000 do 8088 CPU. O chip foi projetado para um ciclo de trabalho de clock de 50%, em comparação com o ciclo de trabalho de 33% usado pelo 8088. Diferenças internas significavam que um V20 poderia completar mais instruções em um determinado tempo do que um Intel 8088 rodando na mesma frequência.

O V20 foi fabricado em tecnologia CMOS de 2 mícrons. Versões anteriores estavam disponíveis que funcionavam em velocidades de 5, 8 e 10 MHz . Em 1990, uma atualização da tecnologia do processo de fabricação resultou no V20H e V20HL, com melhor desempenho e menor consumo de energia. Versões posteriores adicionaram velocidades de 12 e 16 MHz. Os V20HLs também eram completamente estáticos, permitindo que seu relógio fosse interrompido.

O V20 foi descrito como internamente com 16 bits de largura. Ele usou um barramento de dados externo de 8 bits que foi multiplexado nos mesmos pinos do byte inferior do barramento de endereço. Seu barramento de endereço de 20 bits era capaz de endereçar 1 MB.

Foi relatado que o V20 era compatível com o coprocessador Intel 8087 Floating Point Unit (FPU). A NEC também produziu sua própria FPU, a μPD72091.

O V30, uma CPU quase idêntica com um barramento de dados externo de 16 bits, foi lançado em 1o de março de 1984. Era um código-objeto compatível com o Intel 8086.

Extensões ISA

O V20 Instruction Set Architecture (ISA) incluía várias instruções não executadas pelo 8088. Incluíam instruções para manipulação de bits, operações BCD compactadas, multiplicação e divisão. Eles também incluíram novas instruções de modo real do Intel 80286.

Os ADD4S, SUB4Se CMP4Sinstruções foram capazes de somar, subtrair, e comparar enormes embalados codificação binária decimal números armazenados na memória. Instruções ROL4e ROR4gire nibbles de quatro bits . Outra família consistiu das TEST1, SET1, CLR1, e NOT1instruções, que teste, definir, limpar e invertido pedaços individuais de seus operandos, mas são muito menos eficientes do que os posteriores i80386 equivalentes BT, BTS, BTR, e BTC; nem são suas codificações compatíveis. Havia duas instruções para extrair e inserir campos de bits de comprimentos arbitrários ( EXT, INS). E, finalmente, havia dois prefixos de repetição adicionais, REPCe REPNC, que alteravam o original REPEe as REPNEinstruções para digitalizar uma sequência de bytes ou palavras (com instruções SCASe CMPS) enquanto uma condição de menos ou não menos permanecia verdadeira.

O V20 ofereceu um modo que emulava uma CPU Intel 8080 . Uma BRKEMinstrução é emitida para iniciar a emulação 8080. O operando da instrução especifica um número de interrupção cujo vetor contém o segmento: deslocamento onde a emulação deve começar. Para finalizar, uma RETEMinstrução é emitida no código 8080. Um recurso que não costuma ser empregado é o CALLN(chamada nativa), que emite uma chamada de interrupção do tipo 8086 que permite que o código x86 (que retorna usando um IRET) seja misturado ao código 8080.

Outro modo coloca o processador em um estado de economia de energia por meio de uma HALTinstrução.

Processo

Em 1982, a Intel processou a NEC sobre os μPD8086 e μPD8088 deste último. Este processo foi resolvido fora do tribunal, com a NEC concordando em licenciar os projetos da Intel.

No final de 1984, a Intel entrou com uma ação novamente contra a NEC, alegando que o microcódigo no V20 e V30 infringia suas patentes para os processadores 8088 e 8086. O engenheiro de software da NEC, Hiroaki Kaneko, estudou o design de hardware das CPUs da Intel e o microcódigo original da Intel.

Em sua decisão, o tribunal determinou que o microcódigo da loja de controle constitui um programa de computador e, portanto, está protegido por direitos autorais. Eles descobriram ainda que a Intel havia perdido seus direitos autorais ao negligenciar a garantia de que todos os chips de segunda fonte fossem devidamente marcados. O tribunal também determinou que a NEC não copiou simplesmente o microcódigo da Intel e que o microcódigo no V20 e no V30 era suficientemente diferente do da Intel para não infringir as patentes da Intel.

Essa decisão estabeleceu a legalidade da engenharia reversa.

Variantes e sucessores

| Produtos: | Parte no: | Detalhes: |

|---|---|---|

| NEC V30 | μPD70116 | Essencialmente um NEC V20 com um barramento de dados externo de 16 bits, o V30 era compatível com o Intel 8086 . O V30 foi uma atualização de fábrica do 8086 usado no switch de escritório central GTD-5 EAX Classe 5. Também foi usado no Psion Series 3 , no NEC PC-9801 VM, no Olivetti PCS86, no Olivetti PC1, no cartão "PC Transporter" da Applied Engineering para a série de computadores Apple II e em várias máquinas de fliperama (especialmente aquelas fabricadas por Irem ) no final dos anos 1980. Anos mais tarde, uma versão de baixa voltagem foi usado em Bandai handheld 's WonderSwan consola de jogos. |

| NEC V20HL | μPD70108H | Versão de alta velocidade (até 16 MHz) e baixa potência do V20. |

| NEC V30HL | μPD70116H | Versão de alta velocidade (até 16 MHz) e baixa potência do V30. |

| NEC V25 | µPD70320 | Uma versão microcontrolada do NEC V20. |

| NEC V25HS | μPD79011 | Uma versão do V25 com o RX116 RTOS na ROM interna. |

| NEC V25 + | μPD70325 | Versão de alta velocidade do V25. |

| NEC V33 | Uma versão do V30 com endereços e barramentos de dados separados e cuja decodificação de instruções é feita por lógica física em vez de um armazenamento de controle microprogramado. O rendimento é duas vezes mais alto que um V30 para a mesma frequência de clock. O V33 tem desempenho equivalente ao Intel 80286 . O espaço de endereço de memória foi aumentado para 16 MB. Duas instruções adicionais BRKXAe RETXAsuportam o modo de endereçamento estendido. A emulação 8080 não é suportada.

|

|

| NEC V33A | μPD70136A | É diferente do V33 por ter números de vetor de interrupção compatíveis com os processadores 80X86 da Intel. |

| NEC V35 | μPD70330 | Uma versão microcontrolada do NEC V30. |

| NEC V35HS | μPD79021 | Uma versão do V35 com o RX116 RTOS na ROM interna. |

| NEC V35 + | μPD70335 | Uma versão de alta velocidade do V35. |

| NEC V40 | μPD70208 | Uma versão embarcada do V20, integrado 8251 USART compatível com Intel , temporizador de intervalo programável 8253 e interface de porta paralela 8255 . Usado no Olivetti PC1, Digisystems Jetta XD e Zenith EZ-PC. |

| NEC V40HL | μPD70208H | Uma versão de alta velocidade e baixa tensão do V40. |

| NEC V50 | μPD70216 | Uma versão incorporada do V30. É a CPU principal do Akai S1000 e S1100, e do Korg M1 . |

| NEC V50HL | μPD70216H | Uma versão de alta velocidade e baixa tensão do V50. |

| NEC V41 | μPD70270 | Integra um núcleo V30HL e periféricos PC-XT : interface de porta paralela 8255 , temporizador de intervalo programável 8254 , PIC 8259 , controlador DMA 8237 e controlador de teclado 8042 . Também integra controlador DRAM completo. Foi usado no Olivetti Quaderno XT-20. |

| NEC V51 | μPD70280 | Integra um núcleo V30HL e periféricos PC-XT : interface de porta paralela 8255 , temporizador de intervalo programável 8254 , PIC 8259 , controlador DMA 8237 e controlador de teclado 8042 . Também integra controlador DRAM completo. Foi usado no Olivetti Quaderno XT-20. |

| NEC V53 | μPD70236 | Integra um núcleo V33 com DMA de 4 canais (μPD71087 / i8237), UART (μPD71051 / i8251), três temporizadores / contadores (μPD71054 / i8254 ) e controlador de interrupção (μPD71059 / i8259 ). Foi usado na Akai MPC3000 e Akai SG01v . |

| NEC V53A | μPD70236A | Integra alguns periféricos com um núcleo V33A. |

| NEC V55PI | μPD70433 | |

| Vadem VG230 | Uma plataforma de PC de chip único. O VG230 continha um processador NEC V30HL de 16 MHz e lógica de núcleo compatível com IBM PC / XT, controlador de LCD (CGA / AT & T640x400) com suporte para plano de toque, scanner de matriz de teclado, controlador de cartão PCMCIA 2.1 duplo , suporte de hardware EMS 4.0 para até 64 MB e temporizador integrado, controladores PIC, DMA, UART e RTC. Foi usado no HP OmniGo 100 , 120 e IBM Simon . | |

| Vadem VG330 | Sucessor do VG230, ele continha um processador NEC V30MX de 32 MHz e um núcleo lógico compatível com IBM PC / AT com PICs duplos, controlador LCD (640x480), scanner de matriz de teclado, controlador PC Card ExCA 2.1 e porta SIR. | |

| NEC V60 | Começando com o processador V60, a NEC se afastou do design x86. |

- Morrer fotos

Veja também

- NEC RX116 , RTOS de 16 bits baseado em ITRON -1 dedicado

- NEC μPD9002 , uma CPU compatível com Z80 e x86

Referências

Leitura adicional

- Manual do usuário V20 / V30 ; NEC; 228 páginas; 1986. (arquivo)

- Davis, Randy (dezembro de 1985 - janeiro de 1986). Escrito em Greenville, Texas, EUA. "Os novos microprocessadores NEC - 8080, 8086 ou 8088?" (PDF) . Micro Cornucopia (27). Bend, Oregon, EUA: Micro Cornucopia Inc. pp. 4-7. ISSN 0747-587X . Arquivado (PDF) do original em 11/02/2020 . Página visitada em 2020-02-11 .

links externos

- Buchty, Rainer. "Casiorama" . www.buchty.net .

- "NEC V20" . cpu-collection.de .

- Hinckley, Robert C. (janeiro de 1987). "NEC v Intel:. Will Hardware ser arrastado para o buraco negro de Editores de direitos autorais ' " . Revista de Direito de Alta Tecnologia de Santa Clara . Vol. 3 não. 1. pp. 23–72.