Lógica do transistor de passagem - Pass transistor logic

Em eletrônica , a lógica do transistor de passagem (PTL) descreve várias famílias lógicas usadas no projeto de circuitos integrados . Ele reduz a contagem de transistores usados para fazer portas lógicas diferentes , eliminando transistores redundantes. Os transistores são usados como interruptores para passar os níveis lógicos entre os nós de um circuito, em vez de como interruptores conectados diretamente às tensões de alimentação. Isso reduz o número de dispositivos ativos, mas tem a desvantagem de que a diferença de tensão entre os níveis lógicos alto e baixo diminui a cada estágio. Cada transistor em série é menos saturado em sua saída do que em sua entrada. Se vários dispositivos são encadeados em série em um caminho lógico, uma porta convencionalmente construída pode ser necessária para restaurar a tensão do sinal para o valor total. Em contraste, a lógica CMOS convencional comuta os transistores para que a saída se conecte a um dos trilhos da fonte de alimentação, de forma que os níveis de tensão lógica em uma cadeia sequencial não diminuam. A simulação de circuitos pode ser necessária para garantir um desempenho adequado.

Formulários

A lógica do transistor de passagem geralmente usa menos transistores, funciona mais rápido e requer menos energia do que a mesma função implementada com os mesmos transistores em lógica CMOS totalmente complementar.

O XOR tem o mapa de Karnaugh do pior caso - se implementado a partir de portas simples, ele requer mais transistores do que qualquer outra função. Os projetistas do Z80 e de muitos outros chips economizaram alguns transistores implementando o XOR usando lógica de transistor de passagem em vez de portas simples.

Princípios básicos de circuitos de transistor de passagem

O transistor de passagem é acionado por um sinal de relógio periódico e atua como uma chave de acesso para aumentar ou diminuir a capacitância parasita C x , dependendo do sinal de entrada V in . Assim, há duas operações possíveis, quando o sinal do relógio está ativo (CK = 1) são a transferência lógica "1" (carregando a capacitância C x para um nível lógico alto) e a transferência lógica "0" (carregando o capacitância C x para um nível lógico baixo). Em ambos os casos, a saída do inversor nMOS de carga de depleção obviamente assume um nível lógico baixo ou lógico alto, dependendo da tensão V x .

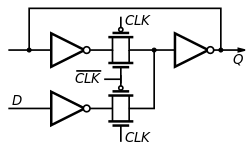

Lógica do transistor de passagem complementar

Alguns autores usam o termo "lógica de transistor de passagem complementar" para indicar um estilo de implementação de portas lógicas que usa portas de transmissão compostas por transistores de passagem NMOS e PMOS.

Outros autores usam o termo "lógica de transistor de passagem complementar" (CPL) para indicar um estilo de implementação de portas lógicas em que cada porta consiste em uma rede de transistores de passagem apenas NMOS, seguida por um inversor de saída CMOS.

Outros autores usam o termo "lógica de transistor de passagem complementar" (CPL) para indicar um estilo de implementação de portas lógicas usando codificação de trilho duplo. Cada porta CPL possui dois fios de saída, tanto o sinal positivo quanto o sinal complementar, eliminando a necessidade de inversores.

Lógica de transistor de passagem complementar ou "Lógica de transistor de passagem diferencial" refere-se a uma família de lógica projetada para certas vantagens. É comum usar esta família lógica para multiplexadores e travas .

A CPL usa transistores em série para selecionar entre os possíveis valores de saída invertidos da lógica, cuja saída aciona um inversor. As portas de transmissão CMOS consistem em transistores nMOS e pMOS conectados em paralelo.

Outras formas

Existem tipos estáticos e dinâmicos de lógica de transistor de passagem, com propriedades diferentes em relação à velocidade, potência e operação em baixa tensão. Conforme as tensões de alimentação do circuito integrado diminuem, as desvantagens da lógica do transistor de passagem se tornam mais significativas; a tensão de limiar dos transistores torna-se grande em comparação com a tensão de alimentação, limitando severamente o número de estágios sequenciais. Como as entradas complementares geralmente são necessárias para controlar os transistores de passagem, são necessários estágios lógicos adicionais.

Referências

Leitura adicional

- Weste e Harris, CMOS VLSI Design, Third Edition ( ISBN 0-321-14901-7 ; ISBN 0-321-26977-2 (edição internacional))

- Douglas A. Pucknell e Kamran Eshraghian, Basic VLSI Design, Third Edition ( ISBN 978-81-203-0986-9 (edição indiana))